本页是介绍 Multi-Gigabit Transceiver (MGT)的系列页面中的第五页。在浏览了很多主题(并列出了一些协议(protocols)和 FPGAs )之后,是时候看看 PMA 如何将数据转换为电信号,反之亦然。

介绍

PMA 由 MGT 中与物理通道相关的部分组成。最值得注意的是, serializer 和 deserializer 是 PMA的一部分。换句话说,物理通道的比特(bits)与并行字之间的转换发生在 PMA内部。

PMA 也是将比特转换为电压的部分。同样,这也是从另一侧的 MGT 接收电压并将其转换为比特的部分。

PMA 的另一个重要作用是补偿电压信号在两 MGTs之间传输时发生的失真:

- 发射机可能会故意扭曲其为传输而创建的模拟信号。发射机的扭曲是试图对信号进行与物理信道相反的操作。这通常被称为 pre-emphasis。

- 接收器的均衡器(equalizer)可以操纵到达的模拟信号,以减轻物理通道造成的失真。

本页介绍了这些功能。 PMA 还负责仅在数据流关闭时才相关的其他任务。这些主题将在下一页讨论。

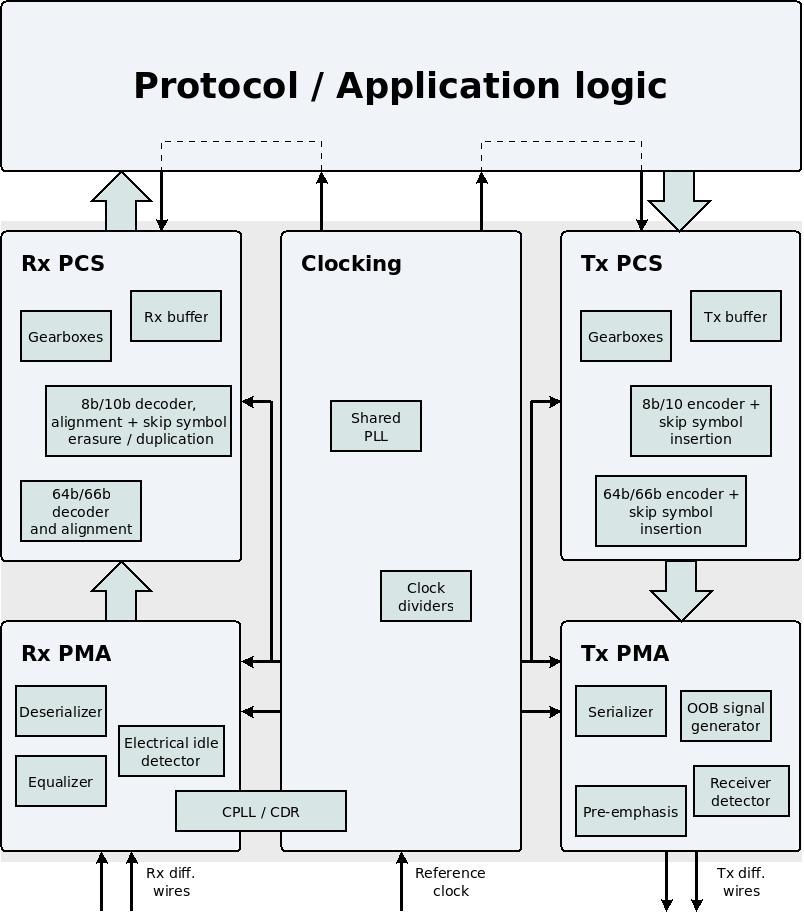

这是典型的 MGT的框图,再次显示在这里以显示 PMA在更大环境中的位置(此图与上一页的图相同)。

与上一页类似,我将使用 Tx PMA 和 Tx PCS 来表示 MGT 中用于传输数据的部分。同样,使用 Rx PMA 和 Rx PCS 来表示用于接收数据的部分。

需要注意的是,在绝大多数使用场景中,无需了解物理通道、它如何扭曲信号以及如何纠正这种扭曲。通常,您需要知道的只是使用均衡器是个好主意。

话虽如此,重要的是要意识到 PMA 在很大程度上是模拟组件。 MGT 通常在 FPGA 芯片上有单独的电源引脚。其中一些引脚为 PMA 供电。这些引脚上的电压通常需要比平常更干净。不满足这些要求可能会显著降低 MGT的性能。

为了便于下文解释,我们将研究 5 Gb/s 通信链路。这是协议(如 SuperSpeed USB Gen 1 和 PCIe 2.0)使用的数据速率。我们还将假设 PMA 和 PCS 之间使用的并行字宽为 32 位。我将从物理通道的简单描述开始,省略本页后面讨论的一些细节。

传输数据

Tx PMA 通过从 LSB开始传输并行字,将并行字转换为电信号。因此,如果比特 0 (bit 0)是“1”,则 Tx PMA 调整其输出引脚(output pins),以便 D+ 和 D- 之间的电压为 500 mV (举例)。如果此比特是“0”,则该电压为 -500 mV (负)。

Tx PMA 等待 0.2 ns,然后对并行字的比特 1 (bit 1)执行相同操作。换句话说, D+ 和 D- 之间的电压将是 500 mV 或 -500 mV,具体取决于比特 1。这样,并行字的每个比特(bits)都在输出引脚上表示 0.2 ns的时间段。在 6.4 ns之后,整个并行字已在线路上传输。 Tx PMA 从 Tx PCS接收一个新的并行字,并开始以相同的方式传输其值。

并行字从 Tx PCS 到 Tx PMA 的传输与时钟(通常称为 XCLK)同步。在这个例子中,这个时钟的时钟周期(clock cycle)是 6.4 ns,所以它的频率是 156.25 MHz。毫不奇怪,是 156.25 × 32 = 5000。

我这里描述的是 SERDES的发送端。分配给这 SERDES的输出(output)的每个比特的时间是 0.2 ns,因此数据速率为 5 Gb/s。

在这个例子中,两个差分输出引脚之间的电压是 500 mV。这在 PCIe 和 SuperSpeed USB的允许范围内。请注意,协议规范以及 MGT的数据手册(datasheets)通常以 differential peak-to-peak voltage的形式指定此电压。这是最低和最高差分电压之间的差值,即本例中的 -500 mV 和 500 mV 之间的差值。因此对于这个例子, differential peak-to-peak voltage 是 1000 mV。这是规范中通常会出现的数字和数据手册。

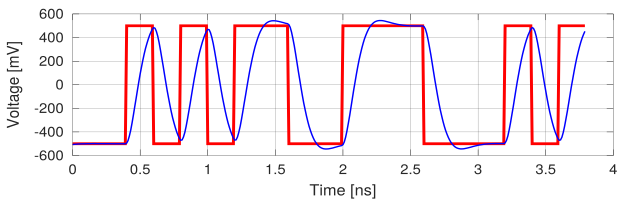

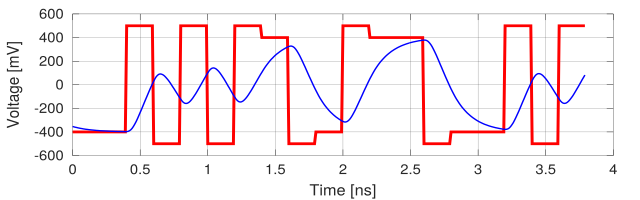

但信号到达接收器时已经发生了变化。下图显示了模拟信号的波形的示例:

发射器的输出( D+ 和 D-之间的电压)显示为红色。蓝色波形是此信号如何到达接收器的示例。此示例显示了带宽为 2.5 GHz的简单 low-pass 滤波器的模拟。

在本页中,我将依赖此示例,其数据速率为 5 Gb/s ,差分电压为 500 mV。当然也可以使用其他数字: FPGA MGT 允许控制数据传输速率和输出电压。

eye diagram

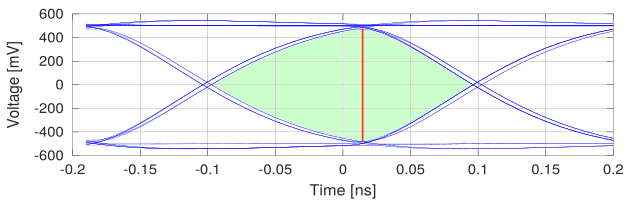

上图中的波形表明到达接收器的信号与发射器产生的信号不同。 eye diagram 是到达接收器的信号的图形表示。此图是通过在同一轴上绘制多个波形创建的。每个这样的波形都是传输的比特随机组合的结果。因此,图上重叠的波形代表到达信号的所有可能形状。

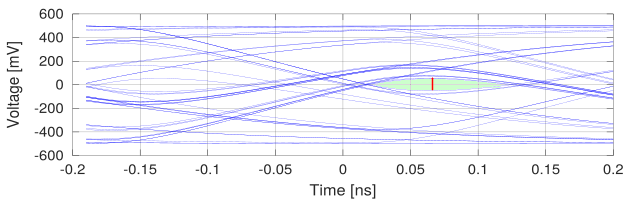

这是与上图相同场景的 eye diagram :

这张图片解释了为什么它被称为“eye diagram”。中间的绿色区域呈眼睛的形状。

红线显示了测量电压的最佳时机,目的是确定传输的比特是“0”还是“1”。此时电压差最大,因此此时抗噪性最好。请注意,所选时刻略晚于零。将其与上一张图片进行比较: 此时检测到的比特在 0.2 ns时已经传输完毕,检测时间甚至稍晚一些。

eye diagram 通常用于评估到达接收器的信号质量。此图通常在传输信号的物理介质的模拟中创建。也可以借助示波器或更专业的测量设备从实际信号的测量中获得 eye diagram 。

接收数据

Rx PMA 将电信号转换成并行字: Rx PMA 每 0.2 ns个时间周期测量一次它的两个输入引脚(D+ 和 D-) )之间的电压,如果这个电压为正,那么这个并行字的比特 0 就被赋值为 '1',否则这个比特就是 '0'。 Rx PMA 继续给并行字的另一个比特赋值,从比特 1 一直到比特 31(bit 31),当并行字完成之后, Rx PMA 就把它交给 Rx PCS,所以 Rx PMA 是 Tx PMA的镜像。

但是 Rx PMA 如何知道何时测量输入引脚的电压?这应该在 0.2 ns的每个时间段内发生一次,但是在这个时间段内具体什么时候发生呢? Rx PMA 如何知道上图中 eye diagram 中红线所示的最佳时间?

事情变得更加复杂的是, Rx PMA 通常无法访问 Tx PMA 所依赖的参考时钟(reference clock)。因此,接收方对 0.2 ns 持续时间的感知与发送方对同一问题的看法并不完全相同。此外,由于抖动(jitter),这个参考时钟(reference clock)的频率一直在随机变化。而对于需要 SSC (Spread Spectrum 时钟)的协议,这个时钟的频率会根据预定义的模式故意连续变化。

这个问题的解决方案是时钟 Data Recovery (Clock Data Recovery)(CDR)。这是 Rx PMA 内部的一种机制,用于找到对输入引脚上的电压进行采样的最佳时机。 CDR 生成一个采样时钟(sampling clock),该采样时钟(sampling clock)可适应到达的数据流。此时钟除以 32 (在此示例中),目的是生成用于与 Tx PCS接口的时钟。

CDR 对到达的模拟信号中“0”和“1”之间的转换很敏感。更准确地说, CDR 可以检测两个 differential 引脚之间的电压何时在正和负之间变化。这使得 CDR 能够将其生成的采样时钟的频率调整为发射器使用的时钟。

为了正常运行, CDR 需要一个自己的参考时钟。这个参考时钟的频率必须与发射器的时钟频率大致相同。然而,这个参考时钟仅用于与数据流的初始同步。在此初始同步之后, CDR 借助锁相环(PLL)跟随发射器的频率。这种自适应机制不断对采样时钟的频率进行细微更改,以创建发射器时钟的副本。除此之外, CDR 还努力在 0.2 ns的每个周期内将采样(sampling)时刻移动到最优点。换句话说, CDR 试图确保信号的采样发生在上图所示的 eye diagram 中的红线处。

CDR 在获得可靠的通信链路方面起着至关重要的作用。例如,如果发射器使用具有高水平抖动的低质量参考时钟,这将增加每个比特时间周期长度的随机性。如果接收器的 CDR 无法足够快地适应这种随机性,采样将在非最佳位置发生。结果,发生错误的概率会增加。 CDR 也有可能完全失去同步,导致通信链路暂时丢失。这种情况经常被误认为是数据线的 signal integrity 出现问题,而不是低质量的时钟。

在 FPGA MGT中, CDR的行为取决于几个可配置的参数(parameters)。不幸的是,这些参数的含义通常很复杂且没有文档记录。 FPGA 工具根据 MGT的设置自动选择这些参数的值。这特别依赖于数据速率。如果选择了特定的知名协议,则相应地选择 CDR的参数。有时测试不同的设置以获得更稳定的链接是值得的,特别是如果两 MGTs之间的连接中有低质量的电缆和连接器。

polarity的逆转

Rx PMA 和 Tx PMA 都支持反转物理通道的 polarity 的可能性。这意味着传输“0”而不是“1”,反之亦然。或者在正常情况下接收“0”时接收“1”,反之亦然。

换句话说,如果 D+ 和 D- 的电线互换, MGT 可以弥补这一点。这是一个微不足道但又非常重要的功能,通常可以简化电路板的设计。

信号失真

在理想情况下,来自发射端 MGT 的电压信号会毫无变化地到达接收端 MGT 。但实际上,信号在到达目的地之前会经历多次变化。最值得注意的问题是信号路径的滤波特性: 每次 Tx PMA 在“1”之后传输“0”时,都会出现从正电压到负电压的急剧转变。当然,在从“0”到“1”的转变中,情况正好相反。这种急剧的电压变化被承载信号的物理介质扭曲。电缆和 PCB traces 的行为类似于 low-pass 滤波器。

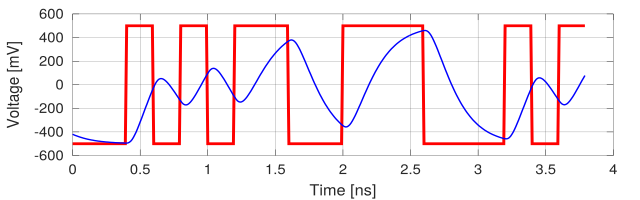

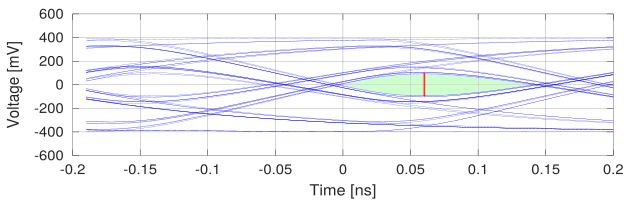

该图与上面的波形示例相同,但模拟了更困难的物理通道:

蓝色的波形表示到达接收器的电压如何“记住”先前传输的几个比特的值。回想一下,接收器需要根据电压是负还是正来决定是“0”还是“1”。因此,来自前一个比特的值会干扰接收器的决定。一个比特的值会干扰接收器对另一个比特的决定,这一事实称为 Inter-Symbol Interference (ISI)。

eye diagram 针对同样模拟的物理通道:

这 eye diagram 表明仍然可以区分“0”和“1”,但差别要小得多。换句话说,只需要很少的噪音就能导致错误。

除了上面的 eye diagram 中模拟的效果之外,信号还以其他方式失真:

- 信号在传输到接收器时会损失能量,因此差分线之间的电压会低于传输的电压。

- 信号从发射器传输到接收器时会产生反射。这种效果类似于声学回声,尤其在信号通过连接器或导电介质的其他突然中断时发生。

- 各种外部源都会给信号添加噪声。这通常不是 MGTs之间通信的主要因素,因为失真的影响通常更为显著。但是,如果电缆较长且隔离性较差,噪声可能会非常显著。

现在我们来看一下减轻物理信道信号失真的两种机制: 均衡器是接收器的一部分, pre-emphasis是发射器的一部分。

均衡器

均衡器处理到达 MGT的模拟信号。该单元的目的是减轻物理通道信号失真的影响。通过这样做,均衡器降低了通道的误码概率并允许更高的数据速率。均衡器始终是 Rx PMA处理链的第一步。

目前主要使用的均衡器有两种。 MGT 可以同时支持以下两种:

- LPM (Low Power Mode)。此均衡器通常由 high-pass 滤波器组成,用于补偿物理信道衰减模拟信号频谱较高部分的趋势。一些 MGTs 会自动调整此滤波器(filter)以适应接收到的信号。对于不太先进的 MGTs,应用逻辑需要从多个可能性中选择一个滤波器(filter)。

- DFE (Decision Feedback Equalizer),下面有更详细的解释。

回想一下上面的例子, Rx PMA 每 0.2 ns个时间段测量一次其两个输入引脚(D+ 和 D-) )之间的电压。根据该电压是负还是正, Rx PMA 检测到“0”或“1”。当使用均衡器时, Rx PMA 依赖于均衡器的输出。

如果使用 DFE ,则假定发送器确保所发送的比特在统计上彼此独立。如果物理通道不扭曲信号会怎样?在这种情况下, Rx PMA 用于决定“0”或“1”的电压在统计上也是相互独立的。换句话说,每次 Rx PMA 检查其 analog input 信号时,都不应与前一个信号或未来的信号存在统计关系。

但实际上,物理通道会扭曲承载数据流的信号。因此,代表“0”或“1”的电压之间存在统计关系: low-pass 滤波器效应会模糊电压信号,反射(“回声”)也会降低信号质量。每个比特的电压电平都会溢出到相邻的比特。如上所述,这种效应称为 Inter-Symbol Interference (ISI)。如果接收器不采取措施减轻 ISI的影响,比特之间的这种相互干扰相当于给信道增加了噪音。

DFE 的工作原理与 echo canceler类似: 它由一个滤波器组成,它可以自我调整,以移除代表“0”或“1”的采样之间的任何 correlation 。更准确地说,它消除了检测到的比特(“0”或“1”)与属于相邻比特的模拟信号之间的相关性。换句话说,如果 DFE 已经实现了其目标,则用于决定比特的值和其他比特的值的模拟信号之间没有统计相关性。在这种情况下, ISI 减少到零,这意味着通道的涂抹效应和反射对传输质量没有影响。

请注意,如果在通道上传输的比特之间存在统计相关性, DFE 将尝试消除这种相关性。因此, DFE 将以与模拟信号的物理通道失真不符的方式调整模拟滤波器。因此, DFE 将扭曲信号而不是修复它。这就是为什么在激活 DFE 时始终需要 scrambler 的原因。

如果无法确保传输的比特相互不相关, LPM 均衡器可能比较合适。 MGT的数据手册通常说明是否可以在没有 scrambler的情况下使用 LPM 均衡器。

并非所有 MGTs 都有 DFE,但几乎所有 MGTs 都有某种类型的 LPM 均衡器。数据手册中的信息通常不完整,无法说明 MGT 支持哪种均衡器,以及这些均衡器的工作方式。如果数据手册没有说明均衡器的类型,则很可能是 LPM。

尽管 DFE 是均衡器的更高级版本,但即使比特彼此不相关, 它的性能也并非总是优于 LPM 。尤其是在物理信道质量较高的情况下, LPM 的性能可能优于 DFE。

Pre-emphasis

操纵发射器的输出信号以改善到达接收器的信号可能会有所帮助。这种方法称为 pre-emphasis,如果信号失真严重,接收器根本无法同步数据流,这种方法尤其有用。这种方法有几种变体,每种 MGT 都有自己的一套功能。

在大多数情况下,物理通道具有 low-pass 滤波器的效果。发射机可以通过塑造发射机的输出信号来主动补偿部分通道失真。最简单的机制是 post-cursor emphasis: 由于物理通道对发射器输出变化的反应较慢,因此发射器会在比特变化时施加更高的电压来补偿这一点。或者更准确地说,发射器会在比特不变时降低电压。

为了演示这种机制,回想一下上面的例子,发送器的输出要么是 -500 mV ,要么是 500 mV (对于“0”或“1”)。

对于 post-cursor emphasis,如果输出从 '0' 变为 '1',则发射器的输出将与之前一样为 500 mV 。但是,如果下一个比特再次为 '1',则输出电压会较低,例如 400 mV。从 '1' 到 '0' 的转换也会发生同样的情况。在这种情况下,输出电压将为 -500 mV。但是,如果下一个比特再次为 '0',则电压将为 -400 mV。

该图显示与上一张图像相同的模拟,使用波形,但应用了 post-cursor emphasis :

红色的波形展示了 post-cursor emphasis 的工作原理: 每次比特变化时,输出电压都会小幅提升,否则会恢复到较低的电压。这种方法通常被称为 de-emphasis,因为发射器会降低重复的比特的电压,因此这些比特是“不太突出”的。

将蓝色的波形与上图进行比较,可以明显看出这个电压的摆幅较小。这似乎不是什么大问题,但在 eye diagram上,差异更加明显:

这显然更好,但还不够好: 在这种情况下仍然需要均衡器。

请注意, post-cursor emphasis 可以描述为简单的 FIR 滤波器。将不带 emphasis 的发射器的电压表示为 x(n) (n 是发射的比特的编号)。每 x(n) 可以具有值 -500 mV 或 500 mV。因此,带有 post-cursor emphasis 的发射器的输出可以写成如下形式:

y(n) = 0.9 x(n) - 0.1 x(n-1)

这是 FIR 滤波器的简单表达式(expression),它更适合高频信号。这可以看作是 low-pass 滤波器物理通道行为的补偿。

表达式“post-cursor emphasis”中的“post-cursor”部分与以下事实相关:相应的 FIR 滤波器可以写成:

y(n) = (1-a) x(n) - a x(n-1)

这个表达式(expression)、 a 一般选为正数。

这个 FIR 滤波器基本上说的是: y(n) 的值主要取决于 x(n),但如果 x(n-1) 具有相同的值,则 y(n) 会更接近于零。 y(n)的操作取决于前一个比特。

因此“cursor”一词与当前传输的比特相关。“post”一词指的是这个滤波器依赖于先前传输的比特,即“cursor”之后的比特。

可以概括出更有利于高频信号的 FIR 滤波器的想法。具体来说,这 FIR 经常在 MGTs中实现:

y(n) = apre x(n+1) + a0 x(n) - apost x(n-1)

在此表达式中, apost 与已经介绍过的 post-cursor emphasis 相关。 apre 表示在“cursor”之前对比特的依赖,即 pre-cursor emphasis,有时也称为 preshoot。这不应与术语 pre-emphasis混淆,后者涵盖了可以用 FIR 滤波器表示的变送器输出信号的整个操作范围。

每 MGT 都提供不同的方法来塑造传输信号。 post-cursor emphasis 通常可用,因为多个协议(protocols)需要它。至于其他变化,则取决于 MGT。

pre-emphasis 的明显缺点是,发射器调整的结果只有接收器可见。回想一下,均衡器可以不断调整自身以实现最佳接收效果。但一般来说, pre-emphasis 机制不知道另一端的信号接收效果如何。这个问题可以通过协议解决。例如, Displayport 协议指定了一种机制,允许接收端向发射器发送请求。这样,接收器就可以控制发射器的电压电平和 post-cursor emphasis的电平。

当预先知道 physical channel 时,Pre-emphasis 也很有用,例如当两 FPGAs 在电路板上相互连接时。即使不知道通道的参数,使用 pre-emphasis 也是一个好主意,尤其是在高数据速率(8 Gb/s 及以上)的情况下。

请注意, pre-emphasis 机制和均衡器不能互相替代,尽管两者都是可以改善信号质量并减少错误的滤波器。均衡器通常是这两者中更强大的工具。 pre-emphasis的作用应该是帮助均衡器或确保信号质量足够好,以使接收器与发射器同步。

在许多应用中,Pre-emphasis 根本不使用。当两 MGTs 之间的距离很长时,尤其是当信号在电路板上传输时,此工具非常有用。当距离相当短且接收器配备了良好的均衡器时,通常没有必要操纵发射器的输出信号。

Statistical eye scan

即使所有数据都无误地到达,我们通常也需要评估信道的质量。特别是,了解信道距离开始产生错误还有多远是很有意义的。信道是否可靠,或者如果物理介质发生最小的变化,就会开始产生错误吗?

此外,请回顾上一页的内容,当信道用于传输有用数据时,无法同时进行 BER 测试。因此,在使用信道时很难评估其质量(某些协议设备会报告所有错误,例如xillyp2p )。

评估链路质量的常用方法是测量接收器上的 eye diagram 。当信号通过电缆和连接器到达时,可以进行此操作: 有专门用于此目的的测量设备(非常昂贵)。但是,当信号通过电路板传输并到达芯片(尤其是 FPGA )时,通常没有地方可以拾取信号。使用 probe 接触电路板上的电线会导致信号形状发生巨大变化,因此测量将毫无意义。

这个问题的优雅解决方案是 statistical eye scan。这意味着 Rx PMA 本身可以测量信号的 eye diagram。这种方法有几个优点:

- 信号的测量点恰好位于 Rx PMA 决定“0”或“1”的位置。

- 测量不会改变信号。

- 测量包括均衡器的校正。因此,它有助于选择使用哪个均衡器(equalizer),并微调其参数。

- 如果 CDR 无法应对发射器时钟的抖动,则可以在本次测量中看到这一点。

- 测量不会干扰 Rx PMA的正常运行。因此,可以在通道传输实际数据时对其进行测试。

这种方法只有一个缺点: 其结果并不是真正的 eye diagram。但结果几乎同样有用。

回想一下, Rx PMA 根据到达信号的差分电压是负还是正来决定接收信号是“0”还是“1”。 CDR 负责以最佳时间做出此决定。

对于 statistical eye scan,还有一个额外的单元负责决定“0”还是“1”。但是,第二个单元的决定时间比第一个单元稍早或稍晚。这个时间偏移是通过设置 MGT的寄存器(registers)来控制的(这可以在 MGT 工作时完成)。

这两个单元之间的另一个区别是它们如何判断信号是“0”还是“1”: 如前所述,第一个单元将信号的电压与零进行比较。第二个单元可以与一系列其他电压阈值进行比较。例如,如果电压阈值选择为 100 mV,则如果接收到的信号高于 100 mV,则第二个单元决定使用“1”。否则,它决定使用“0”。

因此,第二个单元与第一个单元完全相同,但在时间和电压上都有偏移。 MGT 内的逻辑会自动比较指定数量的决策,并计算决策不同的次数。换句话说,如果移动了时序并移动了阈值电压,这个逻辑会计算 Rx PMA对比特的决策会有多少次不同。

如果这两个单元的决策之间没有任何差异,则意味着第二个单元的位置(以时间和电压给出)位于上面 eye diagrams 中标记为绿色的区域内。这种情况在经过一段相当长的测量时间后通过计数结果为零来识别。随着第二个单元的位置接近绿色区域的边缘,计数器的结果变得越来越高。

statistical eye scan 是通过在两个单元之间重复这种具有一系列时间偏移和电压阈值的比较而获得的。这是通过应用逻辑或通过设置 MGT的寄存器到 JTAG来完成的。该过程类似于一个计算机程序,该程序在 for-loop 中运行 for-loop 以获得一系列时间偏移,在 for-loop 中运行 for-loop 以获得一系列阈值电压。完成此操作所需的时间取决于测量的准确性。

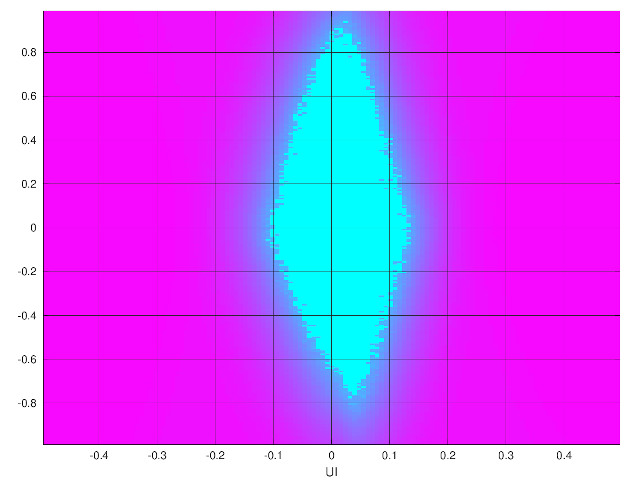

这是一个使用 Artix-7 FPGA获得的 statistical eye scan 示例(取自另一页面)。中间的绿色区域与上方 eye diagrams 中的绿色区域相对应。测量结果与上述所有图像在数量上均有所不同,因为上述示例仅模拟了一种信号失真类型。

获得这样的图像大约需要一分钟。但是,根据在不到一秒的时间内获得的较粗略的图像,可以对通道的质量做出良好的评估。

通常无需设计任何东西即可获得 statistical eye scan。具体来说,此过程可由 Vivado 在 JTAG 连接的帮助下完成。遗憾的是,并非所有 MGTs 都具备 statistical eye scan的功能。