本页是介绍 Multi-Gigabit Transceiver (MGT)的系列页面中的第一页,并概述了本系列的内容。

介绍

Multi-Gigabit transceivers (MGTs)在计算机或电子系统内部不同部件之间的通信中起着重要作用。计算机内部的几个著名接口都是基于 MGTs的,例如 PCIe 和 SATA。其他著名接口用于计算机与其外围设备之间的通信,例如 Gigabit Ethernet、 SuperSpeed USB、 Thunderbolt 和 Displayport。

MGTs 也用于连接电子元件,例如连接两 FPGAs。在这种情况下,通信通常基于不太常见的协议(protocols) ,甚至是某种非标准的协议。但也可以使用 MGTs 将 FPGA 与其他类型的元件连接起来,或者连接其他元件,例如使用Xillyp2p 。

例如,光纤收发器通常是标准模块(特别是 SFP+ 外形尺寸的模块),可直接与 MGTs接口,如本示例设计所示。一些高速 ADC/DACs 也使用 MGTs 来传输采样数据(sample data)(通常基于 JESD204 协议)。一些协议用于传输视频数据(例如,一些 MIPI的物理层使用协议)。

尽管 MGTs 通常用于双向协议,但每 MGT 实际上由两个独立的部分组成: 一个发射器和一个接收器。因此,可以通过关闭两个部分之一来使用 MGT 进行单向传输。对于大多数 FPGA MGTs,还可以独立配置发射器和接收器的参数(parameters)。

综上所述, MGTs 在许多应用中都有使用。通常,接口的名称并不意味着使用了 MGTs (例如 Gigabit Ethernet、 SATA 和 DisplayPort),但物理层由 MGTs组成。

值得一提的是, Xilinx (以及随后的 AMD)对其 MGTs 使用了不同的名称: RocketIO、 GTX、 GTH、 GTY、 GTP、 GTM等。每个名称代表收发器的特定硬件实现,因此这个名称说明了收发器具有的数据速率和其他性能属性。

本系列页面介绍了 MGTs 的基础知识以及与之相关的一些常用技术术语。这样做的目的是让您更容易阅读技术文档,特别是能够识别哪些参数与您的项目相关,哪些参数不相关。

什么是 MGT?

重要的是要认识到,在所有复杂的功能背后, MGT 只是一 SERDES: 它是一种接收和传输数据的电子构件。 MGT与物理世界的电气接口由两根构成差分对的电线组成。当第一根电线(“正”或“正”线)上的电压高于另一根电线(“负”或“负”线)上的电压时,物理状态对应于“1”。否则,它就是“0”。这与差分接口(例如 LVDS)的原理相同。

与 SERDES 的另一个相似之处是 MGT与应用逻辑的接口由并行字组成: 对于应用逻辑的时钟的每个周期,应用逻辑和 MGT之间都会传输一定数量的比特(bits)。这种安排是必要的,因为数据速率远高于 FPGA可能达到的最大时钟频率。

然而,通常的 SERDES 和 MGT之间存在一些重要差异。以下是其中一些:

- MGTs 的数据速率比普通 SERDES高得多。

- SERDES 的接收器需要与数据流一起接收发射器的时钟。另一方面, MGT 接收器可以仅依赖数据流的信号: MGT 会创建一个与数据流的信号相匹配的时钟,并改用这个时钟。此功能称为clock data recovery, CDR 。即使 MGT 接收器可以访问发送器的时钟,它也只能用作参考时钟(reference clock),而不是数据时钟(data clock)本身。

- 在采用 MGT的数据链路上,比特错误(Bit errors)是允许的,属于正常现象。 BER 通常低于 10-12 或 10-15。如果比特错误出现在常规的 SERDES上,则被视为故障,但 MGT则不属于故障。

- 当使用 MGT 时,对在电线对上传输的数据流的内容有限制。数据流始终需要直流平衡。换句话说,数据流上的“0”和“1”的数量平均必须相等。此外,通常要求传输的比特在统计上彼此独立。有关此内容的更多信息,请参见下文。

- MGT 能够产生和检测out-of-band signals (OOBs) 。这些信号是在常规数据流因节能而关闭时传输的。这些信号的目的主要是唤醒另一端的接收器,以便恢复数据比特(data bits)的传输。

那么为什么 MGT 如此复杂?

任何尝试过为 FPGA 项目配置 MGT 块的人都知道,有很多参数和选择。为什么必须这样呢?

其实,这并不复杂: 如本示例设计所示,如果将 MGT 用作 SERDES,则可以消除许多复杂性。

然而,使用 MGT 通常比较复杂,主要有三个原因: 首先,因为 MGT 块实现了许多可以在逻辑阵列(logic fabric)中实现的构建块,但为了提高效率,这些构建块作为 MGT 的一部分实现。例如,所有 MGTs 都具有对8b/10b进行编码和解码的能力,尽管这项任务可以由应用逻辑执行。但由于这种编码技术非常常用,因此 MGT 有能力代替它。

第二个原因与时钟有关: MGT的正常运行需要多个时钟。更复杂的是,与 FPGA的逻辑阵列所用的时钟相比,对时钟(尤其是抖动(jitter))的质量要求更为严格。有时还会使用 SSC (Spread Spectrum Clocking),这让事情变得更加复杂。

因此,正确完成时钟有时候并不比为 MGT 选择正确的参数更容易。

第三个原因是 MGTs 被设计用于支持多种标准通信协议。因此,特定协议所需的功能名称通常取自协议的规范。对于不了解相关协议的人来说,这些术语毫无意义。这使得在为 FPGA设置 MGT 块时很难决定启用哪些功能。

所有这些主题都会在本系列的其余页面中进行更详细的讨论。

注意事项

在大多数用例中, MGTs 用作另一个成熟的协议(特别是 PCIe)的物理层。在这些情况下, FPGA 工具会处理细节,因此无需了解底层发生了什么。

但是,如果您打算将应用逻辑直接连接到 MGT,请务必注意逻辑需要解决的几个挑战。其中一些问题由协议处理,旨在用于 FPGAs之间。

这是要考虑的主题的简短列表。本系列的其余页面将更详细地讨论这些主题。

- 词对齐: 就像任何 SERDES一样, MGT 事先不知道字节或较大字从哪里开始。对于 SERDES,这个问题通常通过尝试一次将并行字移动一个比特(bit)(bit slipping)来解决,直到到达的数据流有意义。基于 MGTs 的协议通常依靠同步字来实现此目的。

- 物理线路上的比特必须是 DC 平衡的。最简单的解决方案是使用 8b/10b 编码,但还有其他有时更合适的可能性。

- Scrambling: 在接收 MGT上使用均衡器(equalizer)几乎总是一个好主意。均衡器可以补偿物理介质的缺陷,从而减少 BER。当数据速率高、使用低成本电缆或物理距离长时尤其如此。但是,某些类型的均衡器要求传输的数据在统计上是随机的: 传输的数据流中不允许一个比特与另一个比特有任何关联。常见的解决方案是使用 scrambler,即在有效载荷数据和比特的伪随机序列之间执行异或(XOR)。接收方使用相同的伪随机序列执行异或,并以此方式获取原始数据流。

- 比特错误: 数据到达接收 MGT时可能会出现错误。接收此数据的逻辑必须设计为能够应对此类错误。在某些应用中,错误被认为很少见,可以忽略(例如,当传输原始视频数据且 BER 低于 10-15时)。在其他应用中,需要错误检测和/或重传机制来确保数据链路可靠。

- 时钟频率之间的区别: 当 MGT 接收数据流时,该信号基于另一侧的时钟(即发送方的时钟)。与接收方可用的时钟相比,该时钟可能具有略微不同的频率。但是, MGT 和应用逻辑之间的接口通常基于本地时钟。因此,如果发送方的时钟比接收方的时钟快,则意味着 MGT 接收数据的速度快于它将数据传送到应用逻辑的速度。结果,这些多余的数据会累积在 MGT 块内,最终发生某种溢出(overflow)。相反,如果到达数据的速率低于本地时钟,则 MGT 无法在每个时钟周期(clock cycle)上传送数据。即使参考时钟随数据流从发送器传递到接收器,也会出现这些问题: 时钟的频率的轻微波动就足以引起此类问题。协议通常借助 idle words来解决此类问题。

- 能源消耗: MGTs 往往耗电很多。部分原因是数据速率高,而高质量的锁相环(PLLs)往往会浪费大量能源。因此,当不使用 MGT 时,即使时间很短,也最好将其关闭。例如,如果在像 50μs一样短的时间内没有传输任何数据, SuperSpeed USB 链路通常会关闭其数据流。然后使用 OOB handshake 在需要时恢复操作。

PMA、 PCS 和时钟

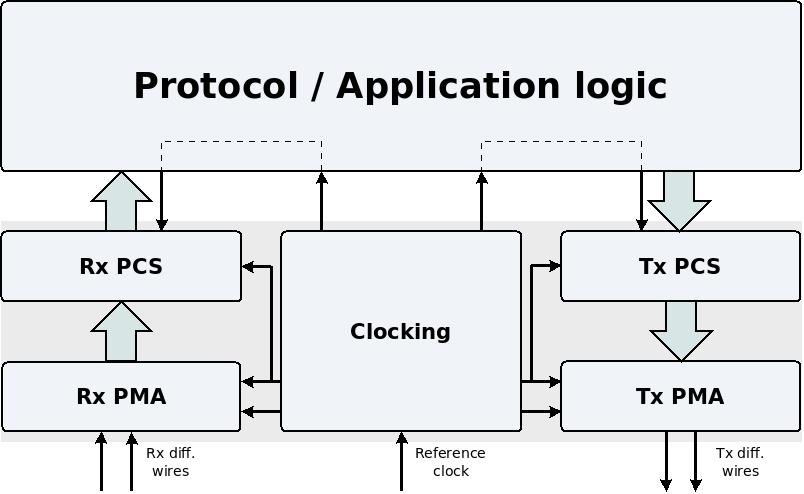

该框图显示了 MGT 的各个部分及其与应用逻辑的交互:

MGT 的功能通常分为三个部分:

- 时钟 : 上面提到,一 MGT的运行需要多个时钟,虽然 FPGA 工具会自动配置这些时钟的参数,但是我们还是需要知道这些时钟是如何生成的。

- PMA (Physical Medium Attachment): 此部分包含 MGT的 SERDES 以及模拟信号子系统(OOB 信号、 receiver detection、均衡器、 pre-emphasis 等)。此部分还实现了 CDR。

- PCS (Physical Coding Sublayer): 此部分包含逻辑,可帮助实现协议通信: 编码器和解码器、字对齐、位宽转换器(gearboxes)、 FIFOs等。 PCS 中的大部分功能可以在逻辑阵列中实现,但为了简单和高效,在 MGT 内部实现。

本系列页面将进一步讨论这些主题。

PIPE 接口

PIPE 标准值得一提: 该标准定义了 MGT 和实现 PCIe、 SuperSpeed USB 或 SATA的逻辑之间的连接。这包括用于传递数据、控制信号和状态信号的端口。

在该标准中, MGT 被称为 PHY 层,而协议被称为 MAC 层。定义 Ethernet、 USB 1.x 和 USB 2.0的标准也使用此术语。这些标准通常由两个单独的芯片实现。例如,为了在处理器芯片上实现 Ethernet , MAC 层在此芯片中实现,而 PHY 层则在单独的芯片中实现。 PIPE 标准以同样的精神编写,尽管 PCIe、 SuperSpeed USB 或 SATA 几乎总是在同一个芯片上完全实现。 PIPE 标准定义的 MAC 层和 PHY 层之间的连接发生在芯片内部,很少对外界可见。

PIPE 标准的一个重要影响是,一个像样的 FPGA MGT 总是会实现 PCIe所需的 PIPE 接口。 SATA 的 PIPE 接口也经常得到支持。这在实现这两个协议(protocols)时显然很有用,但还有另一个重要的好处: 不同的 FPGAs 具有与 MGT类似的界面。特别是,有一些功能元素在几乎所有的 MGTs中都可以找到。

结论

本页概述了 MGT 及其复杂性。在本系列的其余页面中,将解释上述许多概念。但在此之前,我们将从连接两 FPGA MGTs时经常使用的协议的简要概述开始。