本页是介绍 Multi-Gigabit Transceiver (MGT)的一系列页面中的第七页。

介绍

很自然地,配置 FPGA的 MGT 的大部分工作都与数据处理和选择正确的协议(protocol)有关。因此,要正确配置时钟需要花费多少时间和精力可能令人感到惊讶。大部分精力通常用于整理 MGT 相对于其时钟资源(clock resources)提供的不同选项以及它们施加的限制。

由于与 MGT的时钟相关的设计规则在每 FPGA上都不同,因此有关此主题的准确和全面信息的唯一可靠来源是 MGT自己的文档。此类文档通常侧重于机制及其细节,并且可能无法解释为什么这些机制是必要的。本页面试图通过讨论 MGT使用的与时钟相关的概念和挑战来填补这一空白。

锁相环(PLLs)和 VCOs

一般来说,锁相环会将参考时钟(reference clock)的频率与一个常数相乘。这个常数有时是整数,但也可以是小数,也可以小于 1。换句话说,锁相环的输出(output)处的频率可能低于参考时钟的频率。对于与 MGTs一起使用的锁相环,这种情况很少见,但对于锁相环和逻辑阵列(logic fabric),这种情况很有用。

在 FPGA中,有单独的锁相环用于生成 MGTs所需的时钟。锁相环和其他属于逻辑阵列的时钟资源无法支持 MGT所需的频率。特别是, MGT 需要时钟,其频率至少是数据速率的一半。对于低数据速率,所需的频率可能更高。

例如,如果数据速率为 5 Gb/s,则比特时钟(bit clock)通常以 2.5 GHz运行。这是因为 MGT的 SERDES 由时钟边沿(clock edges)(DDR) 激活。但是,如果数据速率相对较低,则 MGT的锁相环中的输出可能会被划分为较低的频率。

几乎所有的锁相环都按照相同的原理工作: 中心部分是 VCO (Voltage Controlled Oscillator),它可以生成具有频率范围的时钟。 VCO的输出插入到将频率除以常数的时钟分频器(clock divider)中。时钟分频器的输出与锁相环的参考时钟进行比较。控制机制会调整 VCO的频率,以使参考时钟和时钟分频器的输出对齐。换句话说,这两个信号具有相同的频率和相同的相位(phase)。

回到 5 Gb/s的例子,我们假设参考时钟的频率是 125 MHz。锁相环的一个可能实现是 VCO的输出除以 20。除法后的信号与参考时钟进行比较并对齐。因此, VCO的频率必须是 2500 MHz,因为 2500 MHz / 20 = 125 MHz。

此创建时钟的方法适用于传输比特(bits): 发送方 MGT 独自决定每个比特(bit)的时间周期的开始和结束位置。但是,当 MGT 接收比特时,另一方决定每个比特的时序。因此,接收方需要适应到达的数据流。如前一页所述,这种适应机制称为时钟 Data Recovery (Clock Data Recovery)(CDR)。 CDR 的实现包括 control loop ,它调整 VCO的频率,以使接收方的时钟与到达的数据流同步。偶尔使用参考时钟来将 VCO 置于足够接近预期频率的初始频率。实现同步后,将忽略参考时钟。

锁相环的使用

FPGA 中的锁相环和 MGTs 是一个复杂的话题。每 MGT 都可以从多个锁相环(PLL)接收其时钟。如果 FPGA 项目中只有一个使用 MGTs 的应用程序,则工具通常会自动选择最合适的锁相环。但是,如果 MGTs 在项目中用于不同用途,则务必确保每 MGT 都连接到最合适的锁相环。

在 FPGA中,通常有锁相环,它们在多 MGTs之间共享。 AMD (Xilinx)将它们称为 QPLL,而 Altera 则有 fPLL 和 ATX PLL。另一方面,还有锁相环,它们是特定 MGT的本地锁相环。它们被称为 CPLL (AMD / Xilinx)或 CMU 锁相环(Altera)。与共享的锁相环相比,本地锁相环通常质量较低且功能较少。不同之处在于频率、抖动(jitter)的范围,以及相对于参考时钟可以选择哪些乘法比率。

每 FPGA 都有一套复杂的规则,定义锁相环和 MGTs 可以如何互连。这些规则还定义了将锁相环连接到 FPGA的参考时钟输入(reference clock inputs)的可能性。因此,不能想当然地认为所有 MGTs 都可以连接到它们所需的时钟。这与逻辑阵列的时钟非常不同,后者几乎没有任何限制。

因此,建议在决定为每 MGT选择哪个锁相环之前仔细阅读数据手册(datasheet)。特别是,在设计电路板时,验证是否可以为所有 MGTs 提供其时钟非常重要。这可以通过创建包含所有必需 MGTs的 FPGA 项目来实现,并确保该项目的实现(implementation)成功,并且所有引脚都放置在正确的位置。

参考时钟

FPGA 具有单独的引脚,用于参考时钟,后者用于 MGTs的锁相环。在电路板设计中,重要的是要验证参考时钟输入是否可以与时钟所针对的 MGTs 一起使用。参考时钟输入、锁相环和 MGTs 之间的互连不允许所有可能的组合。允许的组合在 FPGA的文档中进行了描述,但很难得出明确的结论,因为规则可能很复杂。通常最好在 FPGA 项目的帮助下确保满足需求。

用于此目的的时钟必须具有高精度和低噪声的抖动。连接由通用时钟芯片生成的时钟是一种常见错误。这样做可能会降低 MGT的性能,并产生看起来像信号完整性问题或数据线上增加噪音的故障。

如果 MGT 是为特定的协议(例如 PCIe、 SuperSpeed USB 或 SATA)设计的,建议阅读 FPGA 制造商关于参考时钟要求的文档。标有“low-jitter clock source”的几个电子元件可能不够好。

抖动是一个随机过程。抖动的幅度是一个重要参数,但并不总是一个充分参数。时钟的抖动的随机性可能导致时钟周期(clock cycle)发生快速变化,而这些变化也可能很慢。抖动在这方面的表现可以从抖动的 noise spectrum中推断出来。

产生时钟的组件的数据手册有时仅给出抖动幅度的数字(通常以 picoseconds为单位)。通常无法获得有关抖动的 noise spectrum 的信息。尽管缺乏这些信息,但这样的组件可能还是足够的,特别是如果抖动的幅度本来就非常低的话。这个问题通常没有简单的答案。

然而,参考时钟的质量对于 MGT的任何用途都很重要。众所周知的协议要求是一个很好的参考,可用于任何项目。与 development boards上用作参考时钟的组件进行比较也很有用。

时钟换成逻辑阵列

用于 MGT 和逻辑阵列之间接口的时钟源自 MGT自己的锁相环。这是必要的,因为在 PMA 内部, SERDES 依赖于两个时钟 : 时钟对应物理通道上的比特,以及与并行字一起使用的时钟。为了使 SERDES 正常工作,这两个时钟必须在 PMA内部对齐。

另一方面,逻辑阵列使用的任何时钟都必须以确保较低的时钟偏移(clock skew)的方式进行分配。为此,工具通常会选择全局 clock buffer (global clock buffer)。从 clock buffer 到所有逻辑单元(logic elements)的传播延迟(propagation delay)几乎相等,因此时钟的边沿(edges)同时到达所有目的地。这是允许工具针对逻辑阵列执行正确的时序(timing)计算的必要条件。

尽管这个传播延迟(propagation delay)在所有线(wires)上是一致的,但它并不一定很小。相反,连接 clock buffer 到其目的地的 FPGA 内部的线增加了相当大的时延(delay)。这通常无关紧要,因为所有这些连接之间的差异都很小。

但是这个时延(delay)使得 PMA 使用的两个时钟与逻辑阵列的时钟不对齐。无法借助逻辑阵列的资源对齐这三个时钟,因为其中一个时钟有一个太高的频率。而 MGT 和逻辑阵列必须有一个双方同步的时钟。唯一的解决方案是添加另一个时钟信号。

这可以归结为每个方向必须至少涉及三个时钟信号:

- 时钟与物理通道上的比特同步。此时钟的频率数据速率通常为后者的一半(上例中的2.5 GHz )。

- 与 PMA内部的并行字同步的时钟。这个时钟有时被称为 XCLK。例如,如果 PMA 与 PCS 接口,并行字宽度为 32 比特,则这个时钟就是 156.25 MHz (因为 5000 / 32 = 156.25)。

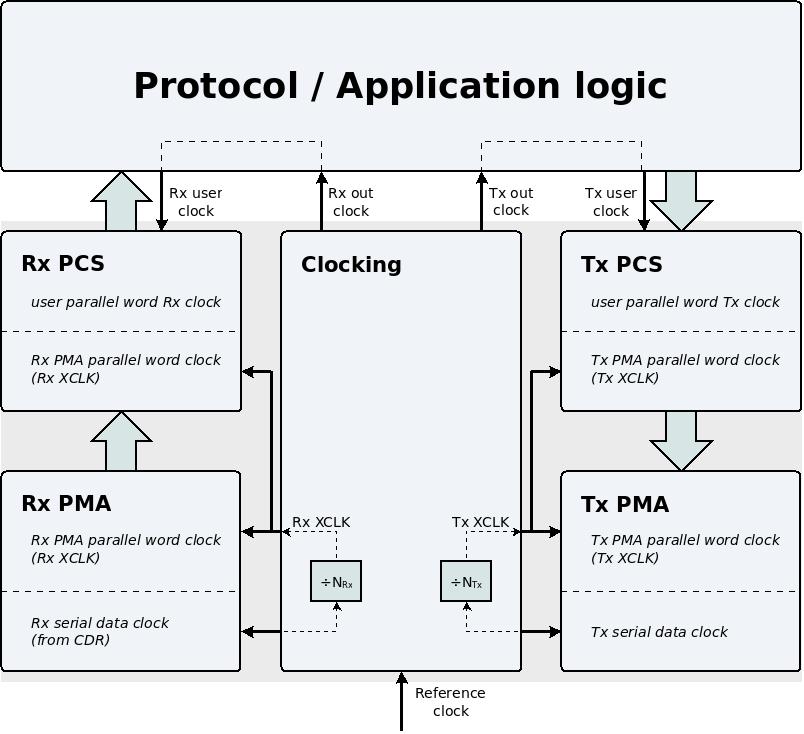

- 逻辑阵列的时钟: 这是与 MGT 和逻辑阵列之间的接口一起使用的时钟。此时钟通常具有诸如 TXUSRCLK2、 RXUSRCLK2、 tx_coreclkin、 rx_coreclkin 和其他类似名称(下图中的“Tx user clock”和“Rx user clock”)。此时钟的频率取决于用于与逻辑阵列接口的并行字的宽度。

请注意,一般来说,时钟是分开的,用于发送和接收。此框图显示了 MGT内部时钟的典型分布:

在这个框图中,每个方向有四个时钟,而不是上面说的三个。接下来会解释这一点。

生成逻辑阵列的时钟

如上所述,逻辑阵列和 MGT 共用的时钟必须与逻辑阵列的 clock buffer一起分发。另一方面,这个时钟必须源自 MGT内部。

我们将从最简单的解决方案开始来解决这两个相互冲突的要求: MGT 确实会生成时钟并使其在输出端口(output port)上可用。此输出端口通常称为 TXOUTCLK、 RXOUTCLK、 tx_clkout、 rx_clkout 等(这是第四个时钟,在上图中称为“Tx out clock”和“Rx out clock”)。此信号进入逻辑阵列 clock buffer(logic fabric clock buffer)的输入。此 clock buffer 的输出是用于在 MGT 和逻辑阵列之间进行接口的时钟信号。

由于这种安排,逻辑阵列的时钟和 MGT 产生的时钟之间的唯一区别是传播延迟和 clock buffer。换句话说, MGT 完全控制逻辑阵列的时钟,但相位除外。如果 CDR的时钟用作与逻辑阵列接口的基础(此选项将在下面讨论),这对于接收数据尤其重要。这是因为 CDR 不断调整这个时钟的频率,以便与到达的数据流保持同步。

如上一页所述, PCS 提供了克服相位、逻辑阵列的时钟和 PMA的时钟之间差异的机制。 Tx buffer 或 Rx buffer 是最简单的选择,但 PCS 也可能具有直接调整此差异的能力。

但是哪个时钟暴露在 MGT的时钟输出端口(clock output port)上?答案自然是 XCLK,因为这个时钟最接近逻辑阵列的时钟上的要求。但是,还有其他几种生成逻辑阵列的时钟的可能性。例如,可以将 MGT的时钟输出(clock output)输入常规逻辑阵列锁相环(logic fabric PLL),以生成具有不同频率的时钟。此锁相环与 clock buffer一起使用,因此时钟信号足以满足其目的。以这种方式使用锁相环开辟了新的可能性,例如 MGT 在其时钟输出端口处穿过其自己的参考时钟。这个时钟的频率可能不适合用时钟来与 MGT接口,但是锁相环可以把这个时钟按必要的比例乘以。

还要注意,逻辑阵列的时钟中的频率可能与 XCLK的频率不同。当 PCS内部激活异步位宽转换器(asynchronous gearbox)时,可能需要这样做。在这种情况下,需要频率差异来补偿 PMA 中以及与逻辑阵列接口中并行字的不同宽度。

与此主题相关的规则很复杂,并且不同 FPGA 之间存在差异。 MGT文档的很大一部分通常用于详细说明不同的可能性。不幸的是,要在时钟上做出正确的决定,需要花时间学习适用于特定 FPGA的规则。

选择逻辑阵列时钟(logic fabric clock)接收数据

当选择如何生成用于接收数据的逻辑阵列的时钟时,需要做出一个基本决定: 此时钟是从 CDR的时钟派生的,还是从固定的参考时钟派生的。换句话说,逻辑阵列的时钟是否适应到达数据流的精确数据速率。

在大多数应用中, MGT 用于双向数据通信。到达的数据和传输的数据之间通常存在密切的关系。例如,传输的数据流可能包括响应到达的数据流而发送的确认和重传请求。在这种应用中,所有逻辑与同一个时钟同步(即所有逻辑都在同一个时钟域(clock domain)中)会很方便。特别是, PIPE 接口要求所有与 MGT 的接口都与单个时钟(在标准文档中称为 PCLK )同步。回想一下,前面说过, PIPE 是 MGTs 和多个协议(protocols)之间的标准接口: PCIe、 SuperSpeed USB 和 SATA。

然而,这种便利是有代价的: 逻辑阵列的时钟的频率可能与 PMA的并行字(即 XCLK的频率)使用的频率略有不同。这种差异导致 PCS内部数据过剩或短缺,因为逻辑阵列接收并行字的速度比这些字到达 PMA的速度慢或快。解决此问题的方法通常是使用 Rx 缓冲区和 skip symbols,如有关 PCS的页面中所述。

或者,逻辑阵列的时钟可以从 PMA的时钟派生而来。采用这种方法,逻辑阵列可以以与数据到达相同的速率消耗数据。当 MGT 仅用于接收数据时,这是一种自然的解决方案。当应用程序逻辑负责处理 clock domain crossing时,这也是双向链路的一种可能选择。Xillyp2p就是一个采用这种方法的协议示例,其完整设计示例对此进行了说明。

AMD FPGA: 两个时钟来自逻辑阵列

AMD FPGAs 上的MGTs (以前称为 Xilinx) 有两个来自逻辑阵列的时钟输入端口(clock input ports),即每个方向有两个端口: TXUSRCLK 和 TXUSRCLK2 用于发送, RXUSRCLK 和 RXUSRCLK2 用于接收。本设计示例中展示了 MGT 的例化(instantiation)版本。

逻辑阵列的几乎所有接口都与 TXUSRCLK2 或 RXUSRCLK2 同步(取决于方向)。另外两个输入、 TXUSRCLK 和 RXUSRCLK 仅在 PCS的某些部分内部使用。

TXUSRCLK 通常与时钟信号和 TXUSRCLK2相同。但是, AMD的 FPGAs 中的 MGTs 具有一项功能,允许与逻辑阵列接口中使用的并行字宽是 PCS内部的两倍。使用此功能时, TXUSRCLK的频率是 TXUSRCLK2的频率的两倍。这是使用逻辑阵列锁相环的另一个原因。

同样的原理也适用于 RXUSRCLK 和 RXUSRCLK2。

概括

本页简要介绍了与 MGT的时钟相关的几个主题。然而,了解 MGT的具体功能和限制是必要的,以便就 MGT的时钟资源的使用做出明智的决定。希望本页中的解释有助于理解 MGT的时钟应该如何工作和相互交互。

关于 MGTs的系列文章到此结束,第七页到此结束。下一页将讨论硬件流控制(flow control),为本系列文章画上句号。