介绍

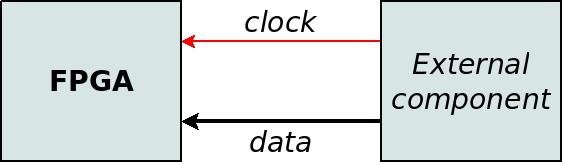

本页讨论 source-synchronous data 输入: 这种技术意味着数据输入(data inputs)与外部组件与这些输入并行生成的时钟同步。

通常使用此方法只是因为这是外部组件的工作方式。另一个很好的理由是数据(data)的来源在物理上远离 FPGA。 FPGA 和另一侧之间也可能有电缆和连接器。例如,发送像素数据(pixel data)的 digital camera 。

source-synchronous 时钟的一个可能困难是它可能不会一直处于活动状态。时钟信号也可能受到悬空物理连接或过大噪音的影响。也有可能是时钟没有稳定的时钟周期(clock period),或者抖动(jitter)过高。当数据(因此也是时钟)的来源是处理器的 I/O peripheral时,这种情况经常发生。

请注意,有一个单独的页面总体上讨论了时钟和数据之间的关系。

应对不稳定的时钟

source-synchronous 输入最重要的准则是时钟不应直接连接到 FPGA内部的逻辑单元(logic elements)。相反, FPGA 内部使用的时钟应该是干净的时钟,它是由 FPGA内部的锁相环(PLL)生成的。

如果外接的时钟直接连接到 FPGA内部的逻辑,可能会出现奇怪的问题: 损坏的时钟会产生意外行为,而这些行为看起来不像是时钟的问题。过多的抖动和 glitches 可能会违反确保设计可靠运行的时序(timing)要求。结果是几乎任何事情都可能发生,包括根据 Verilog 代码不可能出现的情况。因此很容易误以为问题出在 FPGA 设计中的 bug 。

很自然地(错误地)认为时钟的问题只会导致时钟周期的丢失,因此一些数据元素将会丢失。当一个坏的时钟导致其他问题时,解决这个问题的尝试通常集中在逻辑设计上看起来最相关的部分。那会浪费很多时间。

唯一可以让逻辑阵列(logic fabric)直接使用外接时钟的情况,就是在保证这个时钟稳定干净的情况下。如果 FPGA 开始运行时此时钟不稳定,则需要处理此问题: 只要时钟不稳定,就必须在依赖这个时钟的逻辑上应用一个复位(reset)。

可能的策略

与外部时钟同步主要有四种可能的策略。这些策略将在下面讨论,没有特别的顺序。

策略#1: 01-signal 采样

这个策略对于 source-synchronous 输入来说是最稳健的方法。当外部时钟出现异常时, 01-signal 采样比任何其他方法都有明显的优势。不过这种方法只有当数据源的时钟频率比较低的时候才有用。

该方法将在专门页面上单独讨论。

策略#2: 使用锁相环

通过这种策略,外部时钟连接到 FPGA上的锁相环的输入。这个锁相环(PLL)的输出时钟(output clock)用于逻辑单元。当锁相环未锁定时,将复位信号(reset signal)应用于这些逻辑单元。该解决方案确保逻辑单元依赖稳定的时钟: 当锁相环的输出时钟不稳定时,逻辑单元会被复位(reset)停用。

与直接连接外部时钟相比,锁相环还可以更轻松地实现时序约束(timing constraints): 锁相环补偿了时钟引脚和 FPGA内部时钟之间的时延(delay)。

但是,请注意外部时钟的缺陷可能会导致锁相环的输出(output)处出现过多的抖动。锁相环的 lock detector 可能会继续指示锁相环正常运行,即使它产生的时钟异常嘈杂。这种情况没有简单的解决方案。一种可能性是将时序约束更改为取决于锁相环的输出的逻辑。比如时序约束中的时钟的抖动可以增加到锁相环很可能不会超过的值(因为会出现 loss of lock )。

该策略与system synchronous 时钟有相似之处: 两种场景都是外接一个时钟接一个锁相环, FPGA内部使用这个锁相环的输出。因此,时序约束的编写方式与system synchronous 时钟相同。

请注意,锁相环通常以最适合system synchronous 时钟的方式将其输出时钟与 external 时钟对齐。 source synchronous 时钟的最佳对齐方式可能略有不同。在这两种可能性中,时钟都没有完全对齐。相反,时钟的边沿(edges)之间有一个有意的小时间差。这个时间差更容易满足 I/O 寄存器对时序的要求。某些锁相环可以配置为使时钟与源同步时钟(source synchronous clock)对齐以获得最佳性能。

与此处列出的其他策略相比,此策略是最容易实施的策略。适用于比较高的时钟频率。但对于接近 I/O 所能达到的最大值的频率,此策略可能不起作用。

策略#3: Phase shifting

当传输速率(data rate)接近 FPGA 所能支持的最大值时,通常会选择这种策略。

保证时序要求(timing requirements)在这样的传输速率上不起作用的通常方法: 就不可能实现时序约束。然而,数据信号(data signals)的可靠采样仍然是可能的。

时序约束的问题是通过计算来确保时序要求: 这种计算包括几个不确定的参数,例如 FPGA的制造差异。当考虑这些参数时,计算不会产生可确保可靠采样的时序解决方案。当传输速率非常高时,没有多余的时序可以浪费在这些不确定性上。

但对于特定的 FPGA 芯片,这些参数是恒定的。因此,解决方案是在 FPGA 工作的同时寻找正确的时序。实际上,这意味着 FPGA 内部的状态机(state machine)在数据时钟(data clock)和采样(sampling)时刻之间调整时延。因此,使用自适应机制来找到最佳的时序,而不是依赖于计算。这种机制称为phase shifting 。

这种策略通常与 DDR SDRAM memories和数据信号一起使用。在此应用中,目标始终是尽可能达到传输速率。因此, I/O 端口的功能被推到了极限。因此, phase shifting 是确保数据输入可靠采样的唯一方法: DDR memory 初始化完成后,向 memory 写入一段特殊的数据序列(数据信号到 memory 都是source-synchronous 输出 ,所以时序没有难度)。然后 FPGA 重复读取 DDR memory中的同一部分。状态机通过逐渐改变采样的时延找到最优的时序。预期的输入数据(input data)是已知的,因为它与之前编写的数据序列相同。因此,状态机可以轻松评估数据的可靠性,并找到最佳的时延。

该机制的一个有趣特点是可以忽略 DDR 芯片提供的数据时钟: DDR memory 与 FPGA 生成的时钟同步。这个时钟是 DDR memory收到的source-synchronous 输出的一部分。因此可以保证 source-synchronous 输入的数据时钟具有与 FPGA生成的时钟完全相同的频率。因此,相位 shifting (phase shifting)机制可以依赖内部时钟而不是随数据一起到达的时钟。这两个时钟之间有一个未知的时延并不重要: 不管这个时延(delay)如何,状态机都找到最优的时序。

实际上, DDR memories通常是这样实现这种机制的: 尽管 DDR memories 有一个 source-synchronous 时钟(称为数据 strobe(data strobe)),但相位 shifting 机制的通常实现忽略了这个信号。理由是确保数据信号可靠到达比与 strobe对齐更重要。

所以使用相位 shifting 可以消除对数据时钟的需求。如果保证其频率与传输速率完全相同,则可以依赖内部时钟。

采用这种策略,时序约束的用途与常规 IOB 寄存器相同。

策略#4: 直接使用时钟

这个策略显然是最直接的一个: 外部的时钟直接连接到 FPGA内部的触发器(flip-flops)。是这样的:

module top (

input data_clk,

input [7:0] data

);

reg [7:0] data_samp;

always @(posedge data_clk)

begin

data_samp <= data;

[ ... ]

end

如上所述,这种策略通常不是一个好主意。主要原因是如果 @data_clk 有一 glitch,所有依赖于这个时钟的逻辑都变得不可预测。

如果能保证干净和稳定,以这种方式使用外部时钟是合理的。但即使能保证这一点,由于时钟引脚和触发器之间的时延,实现时序要求可能很困难。一些 FPGAs 具有特殊的时钟资源(clock resources),目的是减少这个时延。这可能需要使用专用的时钟输入引脚(clock input pin)并将 I/O 端口限制在 FPGA上的特定区域。

当直接使用时钟时,时序约束的编写方式与system synchronous 时钟相同。

如上所述,此策略的直接替代方法是使用锁相环。如果数据时钟不稳定,则应考虑 01-signal 采样。

概括

本页首先提到 01-signal 采样并非巧合,并且该策略在单独的页面上进行了描述: 如果传输速率不高于此方法的能力,则这是最推荐的方法。

如果考虑其他策略,一定要注意数据时钟的稳定性。如果时钟偏离其允许的行为(即时钟周期和最大抖动),这可能导致相关逻辑发生永久且不可恢复的故障。只有复位才能使逻辑恢复正常运行。

使用锁相环生成可靠的时钟可以大大改善这种情况: 只要 lock detector 表明如此,锁相环的输出就是可靠的。否则应将复位应用于此逻辑。