종종 저는 모든 registers가 I/O 셀에 삽입되도록 하여 I/O timing을 처리하는 것을 선호합니다. timing이 중요한 곳은 바로 이것이다.

I/O register packing은 Quartus의 기본값이 아닌 것 같습니다. 여하튼, 이 시나리오에 대한 게으른 남자의 레시피는 다음과 같습니다.

이 게시물의 이전 버전에서는 모든 I/Os에서 timing checking을 비활성화할 것을 제안했습니다. 이것은 implementation동안 unconstrained path warning을 무음으로 만들고 특히 Quartus보고서 창의 "TimeQuest Timing Analyzer" 섹션이 빨간색으로 바뀌는 것을 방지합니다.

set_false_path -from [get_ports] set_false_path -to [get_ports]

이것은 좋은 생각이 아닙니다. 특히 input ports와 관련하여 밝혀졌습니다. 이것은 아래에서 더 자세히 설명합니다.

그럼에도 불구하고 registers를 I/O block에 넣으려면 fitter를 설득해야 합니다. QSF에서 추가

set_instance_assignment -name FAST_OUTPUT_REGISTER ON -to * set_instance_assignment -name FAST_INPUT_REGISTER ON -to * set_instance_assignment -name FAST_OUTPUT_ENABLE_REGISTER ON -to *

절대적으로 모든 register에서 이러한 assignments를 만드는 것은 다소 공격적이지만 제대로 작동합니다. fitter는 I/O elements 에 대해 warnings를 발행하여 이러한 constraints를 강제 실행하지 못하는데, 이는 실제로 좋은 일입니다.

얼마나 잘 진행되었는지 확인하려면 fitter report 의 "Resource Section"를 살펴보고( Quartus의 reports pane에서 찾을 수 있음) 적용되는 "Input Registers" 등을 찾으십시오.

차이점은 I/O cells를 포함하는 paths 의 timing reports 에서 분명합니다. 예를 들어, I/O register가 포함된 이 path를 비교하십시오.

+----------------------------------------------------------------------------------+ ; Data Arrival Path ; +---------+---------+----+------+--------+-----------------------+-----------------+ ; Total ; Incr ; RF ; Type ; Fanout ; Location ; Element ; +---------+---------+----+------+--------+-----------------------+-----------------+ ; 2.918 ; 2.918 ; ; ; ; ; data path ; ; 0.000 ; 0.000 ; ; ; 1 ; DDIOOUTCELL_X3_Y0_N32 ; rst ; ; 0.465 ; 0.465 ; RR ; CELL ; 1 ; DDIOOUTCELL_X3_Y0_N32 ; rst|q ; ; 0.465 ; 0.000 ; RR ; IC ; 1 ; IOOBUF_X3_Y0_N30 ; RESETB~output|i ; ; 2.918 ; 2.453 ; RR ; CELL ; 1 ; IOOBUF_X3_Y0_N30 ; RESETB~output|o ; ; 2.918 ; 0.000 ; RR ; CELL ; 0 ; PIN_P3 ; RESETB ; +---------+---------+----+------+--------+-----------------------+-----------------+

DDIOOUTCELL 요소와 register 와 IOOBUF사이의 routing 에 있는 zero increment 에 주목하십시오.

비교를 위해 I/O register가 적용되지 않은 path가 있습니다( logic에 의해 방지되었기 때문에).

+--------------------------------------------------------------------------------+ ; Data Arrival Path ; +---------+---------+----+------+--------+-----------------+---------------------+ ; Total ; Incr ; RF ; Type ; Fanout ; Location ; Element ; +---------+---------+----+------+--------+-----------------+---------------------+ ; 8.284 ; 8.284 ; ; ; ; ; data path ; ; 0.000 ; 0.000 ; ; ; 1 ; FF_X3_Y0_N17 ; Dir_flop_sig ; ; 0.496 ; 0.496 ; RR ; CELL ; 8 ; FF_X3_Y0_N17 ; Dir_flop_sig|q ; ; 2.153 ; 1.657 ; RR ; IC ; 1 ; IOOBUF_X3_Y0_N9 ; DATA[7]~output|oe ; ; 8.284 ; 6.131 ; RF ; CELL ; 1 ; IOOBUF_X3_Y0_N9 ; DATA[7]~output|o ; ; 8.284 ; 0.000 ; FF ; CELL ; 1 ; PIN_T3 ; DATA[7] ; +---------+---------+----+------+--------+-----------------+---------------------+

여기에서 범용 flip-flop이 신호를 생성하여 1.657 ns에 해당하는 routing delay 로 이어지는 방법을 봅니다. 주요 문제는 이 routing delay이 각 implementation마다 다르기 때문에 보드에 signal integrity 문제가 있는 경우 다른 FPGA design 버전이 문제를 해결하거나 다시 나타나게 하기 때문에 FPGA가 원인이 될 수 있다는 것입니다.

Timing constraints

input ports 와 output ports는 모두 timing constraints가 타이트해야 하므로 I/O registers를 최대한 활용하는 것 외에는 만날 수 없습니다. 이것은 원하는 register packing에 문제가 있는 경우 timing failure를 생성할 뿐만 아니라 다음에 설명하는 것처럼 최소 input-to-register timing을 달성하는 데도 필요합니다.

아래 설명은 registers를 구동하는 clock이 외부 clock (즉, clock 에 정수를 곱하는 PLL )와 직접 관련된 경우에만 적용됩니다. registers를 구동하는 clock이 외부 clock와 실질적으로 관련이 없다면 이 게시물에서 설명한 것처럼 상황이 훨씬 더 복잡해집니다.

이 문제를 시연하려면 다음 Verilog code를 고려하십시오.

module top

(

input clk,

input in,

output reg out

);

reg in_d, in_d2;

wire pll_clk;

always @(posedge pll_clk)

begin

in_d <= in;

in_d2 <= in_d;

out <= in_d2;

end

/* Here comes an instantiation of a phase-compensating PLL, which

doesn't change the frequency */

endmodule

또한 SDC file에서 다음 constraint를 고려하십시오.

create_clock -name main_clk -period 10 -waveform { 0 5 } [get_ports {clk}]

derive_pll_clocks

derive_clock_uncertainty

set_input_delay -clock main_clk -max 8.5 [get_ports in*]

set_input_delay -clock main_clk -min 0 [get_ports in*]

이 게시물에서 설명한 것처럼 set_input_delay은 clock 에서 유효한 logic state까지 신호 소스의 최대 delay 입니다. clock의 기간이 10 ns로 설정되어 있으므로 delay constraint를 8.5 ns 로 설정하면 다음 clock이 도착할 때까지( 10 ns에서) 1.5 ns가 허용됩니다. 즉, FPGA의 핀에 있는 setup time 에는 1.5 ns를 초과하지 않도록 하는 constraint가 있습니다.

이 게시물 에서 논의한 것처럼 set_max_delay을 이 용도로도 사용할 수 있습니다(경우에 따라 유일한 방법임).

이것의 compilation (위에 표시된 FAST_INPUT_REGISTER ON QSF 할당과 함께)는 timing report에서 다음 세그먼트를 생성합니다.

+----------------------------------------------------------------------------------+

; Data Arrival Path ;

+---------+---------+----+------+--------+-------------------+---------------------+

; Total ; Incr ; RF ; Type ; Fanout ; Location ; Element ;

+---------+---------+----+------+--------+-------------------+---------------------+

; 0.000 ; 0.000 ; ; ; ; ; launch edge time ;

; 0.000 ; 0.000 ; ; ; ; ; clock path ;

; 0.000 ; 0.000 ; R ; ; ; ; clock network delay ;

; 8.500 ; 8.500 ; F ; iExt ; 1 ; PIN_F2 ; in ;

; 9.550 ; 1.050 ; ; ; ; ; data path ;

; 8.500 ; 0.000 ; FF ; IC ; 1 ; IOIBUF_X0_Y22_N15 ; in~input|i ;

; 9.308 ; 0.808 ; FF ; CELL ; 1 ; IOIBUF_X0_Y22_N15 ; in~input|o ;

; 9.308 ; 0.000 ; FF ; IC ; 1 ; FF_X0_Y22_N17 ; in_d|d ;

; 9.550 ; 0.242 ; FF ; CELL ; 1 ; FF_X0_Y22_N17 ; in_d ;

+---------+---------+----+------+--------+-------------------+---------------------+

output register의 경우와 달리 목록에 "DDIOINCELL" 유형의 flip-flop은 없지만 대신 일반 flip-flop 처럼 보이는 것이 있습니다. 그러나 이 flip-flop 에 대한 배선에는 zero delay (빨간색으로 표시)가 있는데, 이는 flip-flop 와 input buffer가 함께 융합되어 있음을 분명히 나타냅니다.

이 입력에 대한 datasheet report는 다음과 같이 말합니다.

+---------------------------------------------------------------------------------------------------+ ; Setup Times ; +-----------+------------+-------+-------+------------+---------------------------------------------+ ; Data Port ; Clock Port ; Rise ; Fall ; Clock Edge ; Clock Reference ; +-----------+------------+-------+-------+------------+---------------------------------------------+ ; in ; main_clk ; 1.282 ; 1.461 ; Rise ; altpll_component|auto_generated|pll1|clk[0] ; +-----------+------------+-------+-------+------------+---------------------------------------------+ +-----------------------------------------------------------------------------------------------------+ ; Hold Times ; +-----------+------------+--------+--------+------------+---------------------------------------------+ ; Data Port ; Clock Port ; Rise ; Fall ; Clock Edge ; Clock Reference ; +-----------+------------+--------+--------+------------+---------------------------------------------+ ; in ; main_clk ; -0.683 ; -0.862 ; Rise ; altpll_component|auto_generated|pll1|clk[0] ; +-----------+------------+--------+--------+------------+---------------------------------------------+

필요에 따라 FPGA 에 필요한 setup time은 constraint에 의해 설정된 1.5 ns 제한보다 낮습니다.

이제 input setup delay을 2 ns로 풀고 나머지는 그대로 두고 compilation을 다시 실행해 보겠습니다.

set_input_delay -clock main_clk -max 6.5 [get_ports in*]

set_input_delay -clock main_clk -min 0 [get_ports in*]

이제 timing report 의 세그먼트는 다음과 같이 말합니다.

+----------------------------------------------------------------------------------+

; Data Arrival Path ;

+---------+---------+----+------+--------+-------------------+---------------------+

; Total ; Incr ; RF ; Type ; Fanout ; Location ; Element ;

+---------+---------+----+------+--------+-------------------+---------------------+

; 0.000 ; 0.000 ; ; ; ; ; launch edge time ;

; 0.000 ; 0.000 ; ; ; ; ; clock path ;

; 0.000 ; 0.000 ; R ; ; ; ; clock network delay ;

; 6.500 ; 6.500 ; F ; iExt ; 1 ; PIN_F2 ; in ;

; 8.612 ; 2.112 ; ; ; ; ; data path ;

; 6.500 ; 0.000 ; FF ; IC ; 1 ; IOIBUF_X0_Y22_N15 ; in~input|i ;

; 7.308 ; 0.808 ; FF ; CELL ; 1 ; IOIBUF_X0_Y22_N15 ; in~input|o ;

; 8.370 ; 1.062 ; FF ; IC ; 1 ; FF_X0_Y22_N17 ; in_d|d ;

; 8.612 ; 0.242 ; FF ; CELL ; 1 ; FF_X0_Y22_N17 ; in_d ;

+---------+---------+----+------+--------+-------------------+---------------------+

뭐? 인터커넥트가 갑자기 1.062 ns로 올라갔다?! register 의 위치는 변경되지 않았으므로 in_d가 I/O register임에는 의심의 여지가 없습니다. 그렇다면 이 지연은 어디에서 왔습니까?

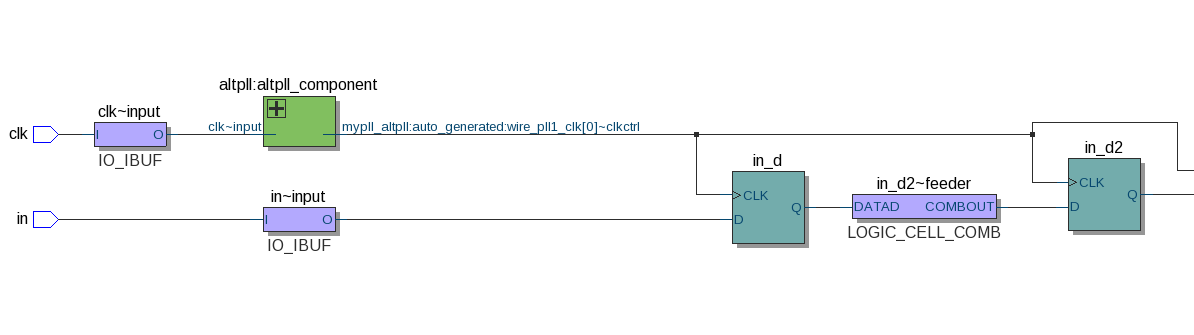

이에 대한 답을 얻으려면 design을 자세히 살펴볼 필요가 있습니다. 전체 compilation 후 Tools > Netlist Viewers > Technology Map Viewer (Post-Fitting)을 선택하면 다음 diagram이 나타납니다(아래에 부분적으로 표시됨, 확대하려면 클릭).

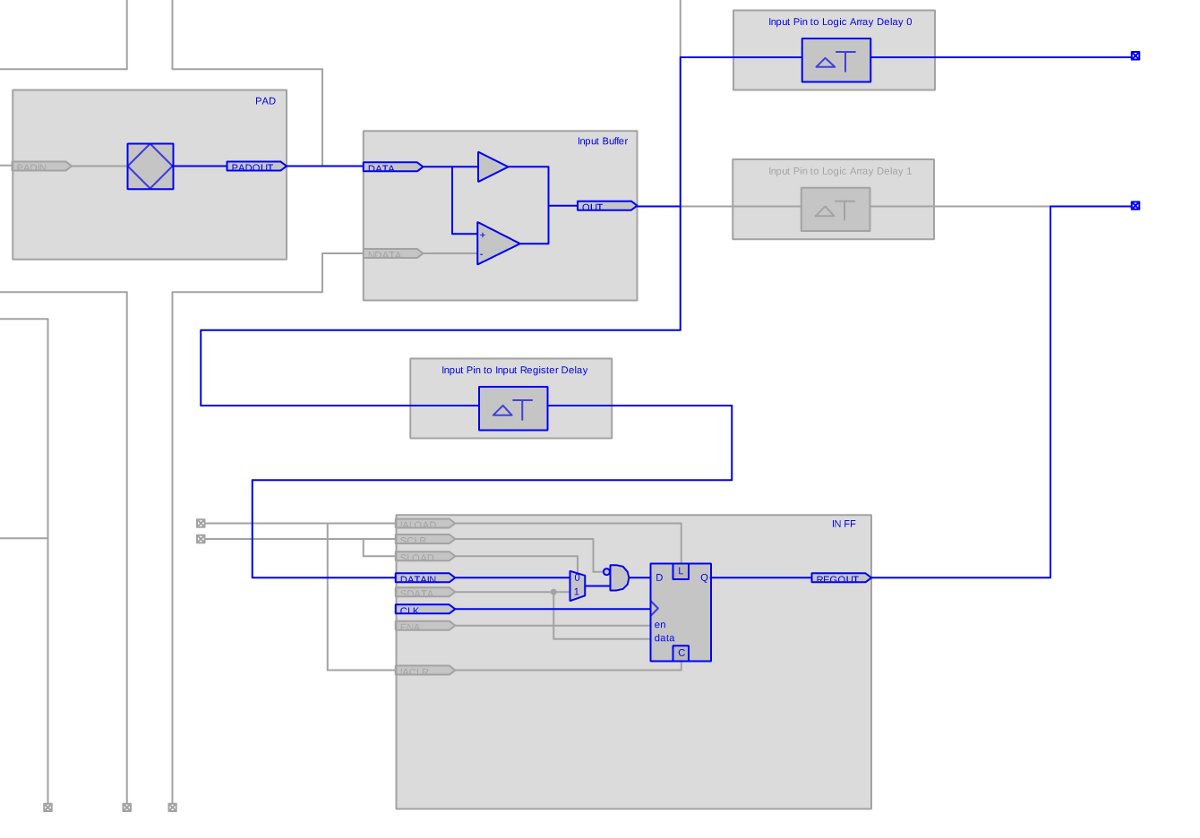

in_d ( register)를 마우스 오른쪽 버튼으로 클릭하고 Locate Note > Locate in Resource Property Editor를 선택하면 다음이 표시됩니다(확대하려면 클릭).

이 도면의 오른쪽(위에 표시되지 않음)에서 "Input Pin to Input Register Delay" 속성은 2로 설정됩니다. 이것이 delay의 이유입니다. constraint가 풀리기 전에는 0로 설정되어 있었습니다. 즉각적인 교훈은 다음과 같습니다.

setup constraint가 기술의 가능한 최상의 가치로 설정되지 않은 경우 Quartus는 비용에 delay을 추가할 수 있습니다.

하지만 왜, Quartus, 왜?

따라서 Quartus가 input pad 와 register사이에 이 delay을 삽입하는 이유가 궁금할 수 있습니다. 가능한 한 빨리 샘플링하는 것이 요점이 아니었나요? 이에 답하기 위해 업데이트된 datasheet report를 살펴보겠습니다.

---------------------+ ; Data Port ; Clock Port ; Rise ; Fall ; Clock Edge ; Clock Reference ; +-----------+------------+-------+-------+------------+---------------------------------------------+ ; in ; main_clk ; 2.205 ; 2.523 ; Rise ; altpll_component|auto_generated|pll1|clk[0] ; +-----------+------------+-------+-------+------------+---------------------------------------------+ +-----------------------------------------------------------------------------------------------------+ ; Hold Times ; +-----------+------------+--------+--------+------------+---------------------------------------------+ ; Data Port ; Clock Port ; Rise ; Fall ; Clock Edge ; Clock Reference ; +-----------+------------+--------+--------+------------+---------------------------------------------+ ; in ; main_clk ; -1.570 ; -1.882 ; Rise ; altpll_component|auto_generated|pll1|clk[0] ; +-----------+------------+--------+--------+------------+---------------------------------------------+

2 ns가 delay constraint에서 축소되었음을 상기하십시오. 따라서 최대 허용 setup time은 1.5 ns 에서 3.5 ns로 증가했습니다. 거의 1 ns의 slack 로 이 요구 사항이 충족되었음을 쉽게 알 수 있습니다.

그래서 Quartus는 "나는 2 ns의 잉여로 setup 요구 사항을 쉽게 충족시킬 수 있습니다. setup time에 1 ns를 추가하고 hold time requirement 에 1 ns를 추가합시다( 0 ns)"와 같이 말했습니다. 그리고 실제로 이 delay에 1.062 ns를 추가함으로써 hold time이 -0.683 ns 에서 -1.570 ns 로 향상되었습니다.

결론: Quartus는 setup 와 hold모두에 대한 마진을 넓혀 jitter에 대한 입력을 더욱 강력하게 만들었습니다. 이것은 상당히 합리적인 일이지만, 이것은 종종 발생하는 것을 원하지도 예상하지도 않습니다.

결론: input 에서 register로 절대적으로 최소한의 delay을 얻으려면 실패한 delay constraint 와 함께 compilation을 실행한 다음 이 실패를 해결할 만큼 constraint를 느슨하게 풉니다. 이렇게 하면 Quartus가 더 나은 hold time을 위해 이 input delay을 추가하여 timing을 "개선"하려고 하지 않습니다.

DDR primitives사용

Intel의 FPGAs 에는 I/O cells 위 또는 근처에 logic이 있어 출력을 생성하고 이중 clock rate에서 입력을 샘플링할 수 있습니다. 이 항목은 관련 사용자 가이드 ug_altddio.pdf에 자세히 설명되어 있습니다. DDR primitive를 인스턴스화(또는 ALTDDIO_BIDIR megafunction사용)하는 것은 도구가 registers를 I/O cells에 넣도록 하는 매력적인 방법입니다. 그러나 반드시 좋은 생각은 아닙니다.

예를 들어 다음과 같은 instantiation :

altddio_bidir ioddr ( .padio(pin), .aclr (1'b0), .datain_h(datain_h), .datain_l(datain_l), .inclock(clk), .oe(oe), .outclock(clk), .dataout_h(dataout_h), .dataout_l(dataout_l), .oe_out (), .aset (1'b0), .combout(), .dqsundelayedout(), .inclocken(1'b1), .outclocken(1'b1), .sclr(1'b0), .sset(1'b0)); defparam ioddr.extend_oe_disable = "OFF", ioddr.implement_input_in_lcell = "OFF", ioddr.intended_device_family = "Cyclone IV E", ioddr.invert_output = "OFF", ioddr.lpm_hint = "UNUSED", ioddr.lpm_type = "altddio_bidir", ioddr.oe_reg = "REGISTERED", ioddr.power_up_high = "OFF", ioddr.width = 1;

결과적으로 양방향 DDR 인터페이스를 구현하는 logic이 생성되지만 timing 에 관한 한 최소한 Cyclone IV에서는 부분적으로 성공합니다. clock-to-output timing은 I/O cell에 포함된 일반 output register 와 정확히 동일하지만 input path 의 지연은 실제로 위의 instantiation 에서 더 나쁩니다. 결과는 다른 Intel FPGA 제품군과 다를 수 있습니다.

DDR primitive로 일반 SDR registers를 모방하려면 datain_h 포트와 datain_l 포트가 동일한 와이어에 연결되어야 하므로 clock의 falling edge는 아무 것도 변경하지 않습니다. 마찬가지로 dataout_l 포트의 값은 falling edge에서 샘플링되므로 무시해야 합니다. 또한 output enable port (oe)는 SDR input 입니다. 제가 이해할 수 있는 한 Intel FPGAs가 있는 DDR rate 로 high-Z를 켜고 끄는 것은 불가능합니다. 적어도 제공된 logic primitives에서는 그렇지 않습니다.

이제 입력이 아닌 output registers에서 잘 작동하는 이유: 힌트는 위의 timing reports 에 있습니다. 일반 I/O cell register의 경우에도 DDIOOUTCELL_Xn_Ym_Nk 구성 요소가 register로 사용됩니다. 즉, DDR output register는 single-rate outputs에도 사용되지만 clock edge는 하나만 사용됩니다. input path의 경우, 위의 timing reports는 logic fabric register (FF_Xn_Ym_Nk)가 사용되었음을 보여줍니다. 핵심은 다음과 같습니다. DDR input logic은 logic fabric 에서도 구현됩니다. 그리고 설상가상으로 DDR의 경우 combinatorial blocks가 I/O cell 와 flip-flop 사이에 끼어 있습니다. 솔직히 말해서 왜 그런 combinatorial block은 단일 입력에서 단일 출력으로의 통과일 뿐인지 이해가 되지 않습니다.

이러한 관찰은 timing reports 와 Quartus의 Post-Fit Technology Map Viewer에 의해 표시된 도면에 의해 뒷받침됩니다. 특히 이러한 정보 소스에서 쓸모없는 combinatorial blocks가 분명합니다.

이 전체 문제는 FPGA family 마다 다를 수 있습니다. Cyclone IV의 경우 출력용으로 DDR primitives 만 사용하는 것이 합리적입니다.

더 중요한 것은 output register가 필요할 때 DDR primitive output이 사용된다는 사실로 인해 다른 출력과 정렬되는 output clock을 생산할 수 있다는 것입니다. 이를 수행하려면 datain_h 포트 및 datain_l 포트에서 각각 일정한 '1' 및 '0' 로 DDR output primitive를 공급하십시오. 다른 출력은 output register 패킹을 사용해야 합니다. 따라서 다른 출력의 토글은 DDR output에서 나오는 clock 의 rising edge 에 맞춰 정렬됩니다.

거의. output clock 의 timing analysis는 다릅니다. clock이 mux를 토글하여 두 output registers 중 어느 것이 출력에 공급되는지 선택하기 때문입니다(자세한 내용은 수평으로 스크롤).

+------------------------------------------------------------------------------------------------------------------------------------+

; Data Arrival Path ;

+---------+---------+----+------+--------+-------------------------+-----------------------------------------------------------------+

; Total ; Incr ; RF ; Type ; Fanout ; Location ; Element ;

+---------+---------+----+------+--------+-------------------------+-----------------------------------------------------------------+

; 0.000 ; 0.000 ; ; ; ; ; launch edge time ;

; 0.000 ; 0.000 ; ; ; ; ; clock path ;

; 0.000 ; 0.000 ; R ; ; ; ; clock network delay ;

; 0.000 ; 0.000 ; R ; ; 1 ; PIN_B12 ; osc_clock ;

; 5.610 ; 5.610 ; ; ; ; ; data path ;

; 0.000 ; 0.000 ; RR ; IC ; 1 ; IOIBUF_X19_Y29_N8 ; osc_clock~input|i ;

; 0.667 ; 0.667 ; RR ; CELL ; 2 ; IOIBUF_X19_Y29_N8 ; osc_clock~input|o ;

; 0.853 ; 0.186 ; RR ; IC ; 1 ; CLKCTRL_G12 ; osc_clock~inputclkctrl|inclk[0] ;

; 0.853 ; 0.000 ; RR ; CELL ; 165 ; CLKCTRL_G12 ; osc_clock~inputclkctrl|outclk ;

; 1.971 ; 1.118 ; RR ; IC ; 1 ; DDIOOUTCELL_X16_Y29_N11 ; sram_controller_ins|ddr_clk|auto_generated|ddio_outa[0]|muxsel ;

; 3.137 ; 1.166 ; RR ; CELL ; 1 ; DDIOOUTCELL_X16_Y29_N11 ; sram_controller_ins|ddr_clk|auto_generated|ddio_outa[0]|dataout ;

; 3.137 ; 0.000 ; RR ; IC ; 1 ; IOOBUF_X16_Y29_N9 ; sram_clk~output|i ;

; 5.610 ; 2.473 ; RR ; CELL ; 1 ; IOOBUF_X16_Y29_N9 ; sram_clk~output|o ;

; 5.610 ; 0.000 ; RR ; CELL ; 0 ; PIN_E10 ; sram_clk ;

+---------+---------+----+------+--------+-------------------------+-----------------------------------------------------------------;

이것은 register-to-pin 분석이 아니라 clock-to-pin입니다. 그럼에도 불구하고 set_output_delay constraint 에는 이 path가 포함됩니다. 그러나 registers 에서 ports까지의 set_max_delay constraint를 사용하는 경우 이 path가 포함되지 않으므로 별도로 처리해야 합니다. 즉, set_max_delay을 사용하는 경우 형식은 다음과 같아야 합니다.

set_max_delay -from [get_clocks main_clk] -to [get_ports sram_clk] 3.8

이제 register로만 구동되는 동일한 voltage standard 등의 다른 pin 와 이것을 비교하십시오.

+----------------------------------------------------------------------------------------------------------------------+ ; Data Arrival Path ; +---------+---------+----+------+--------+-------------------------+---------------------------------------------------+ ; Total ; Incr ; RF ; Type ; Fanout ; Location ; Element ; +---------+---------+----+------+--------+-------------------------+---------------------------------------------------+ ; 0.000 ; 0.000 ; ; ; ; ; launch edge time ; ; 2.507 ; 2.507 ; ; ; ; ; clock path ; ; 0.000 ; 0.000 ; ; ; ; ; source latency ; ; 0.000 ; 0.000 ; ; ; 1 ; PIN_B12 ; osc_clock ; ; 0.000 ; 0.000 ; RR ; IC ; 1 ; IOIBUF_X19_Y29_N8 ; osc_clock~input|i ; ; 0.667 ; 0.667 ; RR ; CELL ; 2 ; IOIBUF_X19_Y29_N8 ; osc_clock~input|o ; ; 0.853 ; 0.186 ; RR ; IC ; 1 ; CLKCTRL_G12 ; osc_clock~inputclkctrl|inclk[0] ; ; 0.853 ; 0.000 ; RR ; CELL ; 165 ; CLKCTRL_G12 ; osc_clock~inputclkctrl|outclk ; ; 1.970 ; 1.117 ; RR ; IC ; 1 ; DDIOOUTCELL_X37_Y29_N11 ; sram_controller_ins|dq_wr_data[6]|clk ; ; 2.507 ; 0.537 ; RR ; CELL ; 1 ; DDIOOUTCELL_X37_Y29_N11 ; sram_controller:sram_controller_ins|dq_wr_data[6] ; ; 5.645 ; 3.138 ; ; ; ; ; data path ; ; 2.717 ; 0.210 ; ; uTco ; 1 ; DDIOOUTCELL_X37_Y29_N11 ; sram_controller:sram_controller_ins|dq_wr_data[6] ; ; 3.182 ; 0.465 ; RR ; CELL ; 1 ; DDIOOUTCELL_X37_Y29_N11 ; sram_controller_ins|dq_wr_data[6]|q ; ; 3.182 ; 0.000 ; RR ; IC ; 1 ; IOOBUF_X37_Y29_N9 ; sram_dq[6]~output|i ; ; 5.645 ; 2.463 ; RR ; CELL ; 1 ; IOOBUF_X37_Y29_N9 ; sram_dq[6]~output|o ; ; 5.645 ; 0.000 ; RR ; CELL ; 1 ; PIN_G14 ; sram_dq[6] ; +---------+---------+----+------+--------+-------------------------+---------------------------------------------------;

전체 clock-to-output 시간은 35 ps만큼 차이가 나지 않지만, 후자의 path는 표면적으로는 완전히 다릅니다. 이것은 우연이 아닙니다. FPGA는 분명히 이러한 유사성을 생성하도록 설계되었습니다. 구체적으로, 위의 timing analysis는 100°C의 온도에서 slow 1200 mV가 지만 이 작은 차이는 다른 분석 조건에서도 일관되게 나타납니다.