이 페이지는 Multi-Gigabit Transceiver (MGT)를 소개하는 일련의 페이지 중 다섯 번째입니다. 많은 주제를 살펴본 후(그리고 FPGAs를 위한 protocols를 나열한 후 ), PMA가 데이터를 전기 신호로 변환하는 방식과 그 반대의 방식을 살펴볼 시간입니다.

소개

PMA는 물리 채널과 관련된 MGT 의 부분으로 구성됩니다. 가장 주목할 만한 점은 serializer 와 deserializer가 PMA의 일부라는 것입니다. 즉, 물리 채널의 bits 와 병렬 단어 간의 변환은 PMA내부에서 발생합니다.

PMA는 bits를 전기 전압으로 변환하는 부분입니다. 마찬가지로, 이것은 반대편의 MGT 에서 전기 전압을 수신하여 이를 bits로 변환하는 부분입니다.

PMA 의 또 다른 중요한 역할은 이 신호가 두 개의 MGTs사이를 이동할 때 발생하는 전압 신호의 왜곡을 보상하는 것입니다.

- 송신기는 전송을 위해 생성하는 아날로그 신호를 의도적으로 왜곡할 수 있습니다. 송신기의 왜곡은 물리적 채널이 신호에 하는 것과 반대되는 것을 하려는 시도입니다. 이를 종종 pre-emphasis라고 합니다.

- 수신기의 equalizer는 물리적 채널로 인해 발생하는 왜곡을 완화하기 위해 도착하는 아날로그 신호를 조작할 수 있습니다.

이 페이지에서는 이러한 기능을 소개합니다. PMA는 또한 데이터 스트림이 꺼졌을 때만 관련이 있는 다른 작업을 담당합니다. 이러한 주제는 다음 페이지 에서 논의됩니다.

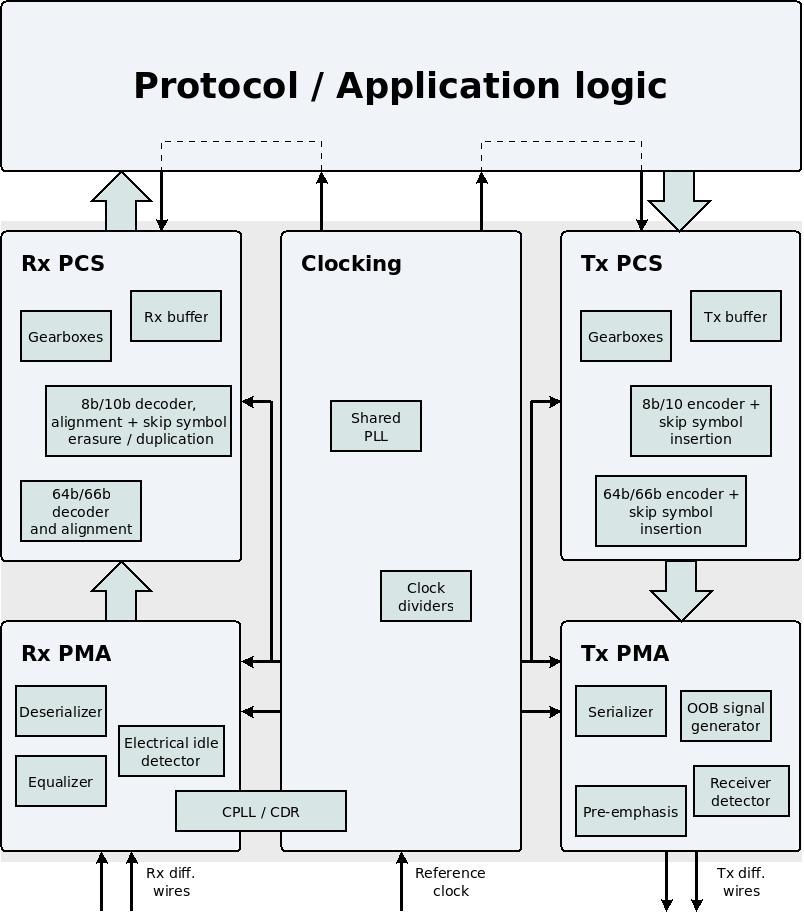

이는 전형적인 MGT의 블록 다이어그램이며, 더 큰 맥락에서 PMA의 위치를 표시하기 위해 다시 한번 표시되었습니다(이 다이어그램은 이전 페이지 의 다이어그램과 동일합니다).

또한 이전 페이지 와 유사하게, 데이터 전송에 사용되는 MGT 의 부분과 관련하여 Tx PMA 및 Tx PCS 라는 표현을 사용할 것입니다. 마찬가지로 데이터 수신을 위한 Rx PMA 및 Rx PCS 도 마찬가지입니다.

대부분의 사용 시나리오에서 물리적 채널, 신호를 왜곡하는 방식, 이 왜곡이 어떻게 수정되는지에 대해 이해할 필요가 없다는 점에 유의하는 것이 중요합니다. 일반적으로 알아야 할 것은 equalizer를 사용하는 것이 좋은 생각이라는 것입니다.

즉, PMA는 상당 부분 아날로그 구성 요소라는 점을 알아두는 것이 중요합니다. MGT는 일반적으로 FPGA chip에 별도의 전원 공급 장치 pins가 있습니다. 이러한 pins 중 일부는 PMA 에 전원을 공급합니다. 이러한 pins 의 전압은 보통보다 더 깨끗해야 합니다. 이러한 요구 사항을 충족하지 못하면 MGT의 성능이 크게 저하될 수 있습니다.

아래 설명을 위해 5 Gb/s 통신 링크를 살펴보겠습니다. 이는 SuperSpeed USB Gen 1 및 PCIe 2.0와 같은 protocols 에서 사용하는 데이터 속도입니다. 또한 PMA 와 PCS 사이에서 사용되는 병렬 단어가 32비트 폭이라고 가정합니다. 이 페이지 아래에서 논의되는 일부 세부 사항을 생략하고 물리적 채널에 대한 간단한 설명부터 시작하겠습니다.

데이터 전송

Tx PMA는 LSB에서 시작하여 병렬 단어를 전송하여 병렬 단어를 전기 신호로 변환합니다. 따라서 bit 0이 '1'이면 Tx PMA는 output pins를 조정하여 D+ 와 D- 사이의 전압이 500 mV (예)가 되도록 합니다. 이 bit이 '0'이면 이 전압은 -500 mV (음)입니다.

Tx PMA는 0.2 ns를 기다린 다음 병렬 단어의 bit 1 에 대해서도 동일한 작업을 수행합니다. 즉, D+ 와 D- 사이의 전압은 bit 1에 따라 500 mV 또는 -500 mV가 됩니다. 이런 식으로 병렬 단어의 각 bits는 0.2 ns의 시간 기간 동안 output pins 에 표현됩니다. 6.4 ns이후에는 전체 병렬 단어가 전선을 통해 전송됩니다. Tx PMA는 Tx PCS에서 새로운 병렬 단어를 수신하고 동일한 방식으로 값을 전송하기 시작합니다.

Tx PCS 에서 Tx PMA 로 병렬 단어를 전송하는 것은 clock (종종 XCLK라고 함)와 동기화됩니다. 이 예에서 이 clock 의 clock cycle은 6.4 ns가 므로 frequency는 156.25 MHz입니다. 놀랍지 않게도 156.25 × 32 = 5000입니다.

제가 여기서 설명한 것은 SERDES의 송신기 측면입니다. 이 SERDES의 output 의 각 bit 에 할당된 시간은 0.2 ns가 며, 이는 5 Gb/s의 데이터 전송률을 가져옵니다.

이 예에서 두 차동 output pins 사이의 전압은 500 mV였습니다. 이것은 PCIe 와 SuperSpeed USB에 허용되는 범위 내에 있습니다. 프로토콜 사양과 MGT의 datasheets은 일반적으로 이 전압을 differential peak-to-peak voltage로 지정합니다. 이것은 가장 낮은 차동 전압과 가장 높은 차동 전압의 차이, 즉 이 예에서 -500 mV 와 500 mV 의 차이입니다. 따라서 이 예에서 differential peak-to-peak voltage는 1000 mV입니다. 이것은 일반적으로 사양과 datasheets에 나타나는 숫자입니다.

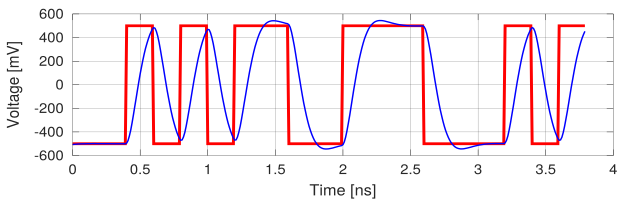

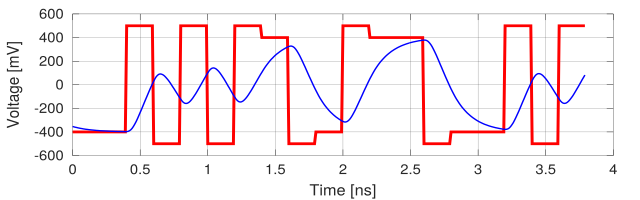

하지만 신호는 수신기에 도착할 때까지 바뀌었습니다. 아래 이미지는 아날로그 신호의 waveform의 예를 보여줍니다.

송신기의 output ( D+ 와 D-사이의 전압)는 빨간색으로 표시됩니다. 파란색 waveform은 이 신호가 수신기에 도달하는 방법의 예입니다. 이 예는 2.5 GHz대역폭을 가진 간단한 low-pass filter 의 시뮬레이션을 보여줍니다.

이 페이지 전체에서 저는 5 Gb/s 의 데이터 속도와 500 mV의 차동 전압을 가진 이 예를 사용할 것입니다. 물론 다른 숫자도 가능합니다. FPGA MGT를 사용하면 데이터 전송 속도와 output 전압을 제어할 수 있습니다.

eye diagram

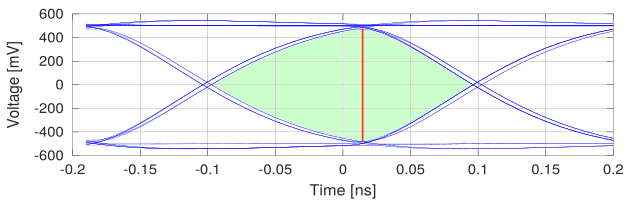

위 이미지의 waveforms는 수신기에 도착하는 신호가 송신기에서 생성된 신호와 다르다는 것을 보여줍니다. eye diagram은 수신기에 도착하는 신호의 그래픽 표현입니다. 이 그래프는 동일한 축에 여러 개의 waveforms를 그려서 만듭니다. 이러한 각 waveform은 전송된 bits의 무작위 조합의 결과입니다. 따라서 그래프에서 겹치는 waveforms는 도착 신호의 모든 가능한 모양을 나타냅니다.

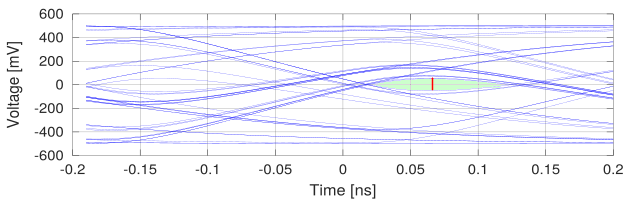

이것은 위 이미지와 동일한 시나리오에 대한 eye diagram 입니다.

이 이미지는 이것이 "eye diagram"라고 불리는 이유를 설명합니다. 가운데의 녹색 영역은 눈 모양입니다.

빨간색 선은 전송된 bit이 '0'인지 '1'인지 판단하기 위한 전압 측정의 최적 타이밍을 보여줍니다. 이때 전압 차이가 가장 크므로 노이즈에 대한 내성이 가장 좋은 시점입니다. 선택한 순간이 0보다 약간 뒤에 있다는 점에 유의하세요. 이전 이미지와 비교해보세요. 이 순간에 감지된 bit은 0.2 ns중에 이미 전송되었으며, 감지는 그보다 약간 늦게 발생합니다.

eye diagram은 일반적으로 수신기에 도착하는 신호의 품질을 평가하는 데 사용됩니다. 이 그래프는 종종 신호를 전송하는 물리적 매체의 시뮬레이션에서 생성됩니다. 오실로스코프나 보다 전문화된 측정 장비의 도움으로 실제 신호를 측정하여 eye diagram을 얻는 것도 가능합니다.

데이터 수신

Rx PMA는 전기 신호를 병렬 단어로 변환합니다. Rx PMA는 두 개의 input pins (D+ 와 D-) ) 사이의 전압을 0.2 ns의 시간 주기마다 한 번씩 측정합니다. 이 전압이 양수이면 병렬 단어의 bit 0 에 '1'가 할당됩니다. 그렇지 않으면 이 bit은 '0'가 됩니다. Rx PMA는 bit 1 에서 bit 31까지 병렬 단어의 다른 bits 에 값을 계속 할당합니다. 병렬 단어가 완료되면 Rx PMA는 이를 Rx PCS에 넘깁니다. 따라서 Rx PMA는 Tx PMA의 거울상입니다.

하지만 Rx PMA는 input pins의 전압을 정확히 언제 측정해야 하는지 어떻게 알 수 있을까요? 이는 0.2 ns의 모든 시간대에 한 번씩 일어나야 하지만 정확히 이 시간대 내에서 언제 일어나야 할까요? Rx PMA는 위의 eye diagram 에서 빨간색 선으로 표시된 최적의 타이밍을 어떻게 알 수 있을까요?

상황을 더 복잡하게 만드는 것은 Rx PMA가 종종 Tx PMA가 의존하는 reference clock 에 액세스할 수 없다는 것입니다. 따라서 수신기가 0.2 ns가 얼마나 오래 지속되는지에 대한 인식은 동일한 질문에 대한 송신기의 견해와 정확히 같지 않습니다. 또한 이 reference clock의 frequency는 jitter로 인해 항상 무작위로 변경됩니다. 그리고 SSC (Spread Spectrum Clock)가 필요한 protocols 의 경우 이 clock의 frequency는 미리 정의된 패턴에 따라 의도적으로 지속적으로 변경됩니다.

이 문제에 대한 해결책은 Clock Data Recovery (CDR)입니다. 이것은 input pins에서 전압을 샘플링하기 위한 최적의 타이밍을 찾는 Rx PMA 내부의 메커니즘입니다. CDR는 도착하는 데이터 스트림에 적응하는 sampling clock을 생성합니다. 이 clock은 Tx PCS와 인터페이스하는 데 사용되는 clock을 생성하기 위해 32 (이 예에서)로 나뉩니다.

CDR는 도착하는 아날로그 신호에서 '0'와 '1' 사이의 전환에 민감합니다. 더 정확하게 말해서, CDR는 두 differential pins 사이의 전압이 양수와 음수 사이에서 변할 때를 감지합니다. 이를 통해 CDR는 생성하는 sampling clock 의 frequency를 송신기에서 사용하는 clock 에 맞게 조정할 수 있습니다.

CDR가 제대로 작동하려면 자체 reference clock이 필요합니다. 이 reference clock의 frequency는 송신기의 clock frequency와 거의 동일해야 합니다. 그러나 이 reference clock은 데이터 스트림과의 초기 동기화에만 사용됩니다. 이 초기 동기화 후 CDR는 PLL의 도움을 받아 송신기의 frequency를 따릅니다. 이 적응 메커니즘은 송신기의 clock의 복제본을 만들기 위해 sampling clock의 frequency를 지속적으로 약간 변경합니다. 그 외에도 CDR는 0.2 ns의 각 주기 내에서 sampling 모멘트를 최적의 지점으로 이동하려고 노력합니다. 즉, CDR는 신호의 sampling이 위에 표시된 eye diagram 의 빨간색 선에서 발생하도록 하려고 시도합니다.

CDR는 신뢰할 수 있는 통신 링크를 얻는 데 중요한 역할을 합니다. 예를 들어, 송신기가 jitter수준이 높은 저품질 reference clock을 사용하는 경우 각 bit의 시간 주기 길이에 무작위성이 추가됩니다. 수신기의 CDR가 이 무작위성에 충분히 빨리 적응하지 못하면 sampling이 최적이 아닌 위치에서 발생합니다. 결과적으로 오류 가능성이 증가합니다. CDR가 동기화를 완전히 잃어 통신 링크가 일시적으로 끊어질 수도 있습니다. 이런 상황은 종종 저품질 clock이 아닌 데이터 와이어의 signal integrity 에 문제가 있다고 오해받습니다.

FPGA MGT에서 CDR의 동작은 구성할 수 있는 여러 parameters 에 따라 달라집니다. 안타깝게도 이러한 parameters 의 의미는 일반적으로 복잡하고 문서화되지 않았습니다. FPGA tools는 MGT의 설정에 따라 이러한 parameters 의 값을 자동으로 선택합니다. 이는 특히 데이터 전송 속도에 따라 달라집니다. 잘 알려진 특정 protocol이 선택되면 CDR의 parameters가 그에 따라 선택됩니다. 특히 두 MGTs사이의 연결을 따라 품질이 낮은 케이블과 커넥터가 있는 경우 더 안정적인 링크를 얻기 위해 다양한 설정을 테스트하는 것이 때때로 효과적입니다.

polarity의 역전

Rx PMA 와 Tx PMA는 모두 물리적 채널의 polarity를 역전할 수 있는 가능성을 지원합니다. 즉, '1' 대신 '0'를 전송하고 그 반대의 경우도 마찬가지입니다. 또는 '0'가 정상적으로 수신될 때 '1'를 수신하고 그 반대의 경우도 마찬가지입니다.

즉, D+ 와 D- 와이어를 바꾸면 MGT가 이를 보상할 수 있습니다. 이는 사소하지만 매우 중요한 기능으로, 종종 PCB 설계를 단순화합니다.

신호 왜곡

완벽한 세상에서는 송신 MGT 의 전압 신호가 아무런 변화 없이 수신 MGT 에 도착할 것입니다. 실제로 신호는 목적지에 도착할 때까지 여러 번 변경됩니다. 가장 주목할 만한 문제는 신호 경로의 필터링 속성입니다. Tx PMA가 '1' 다음에 '0'를 전송할 때마다 양전압에서 음전압으로의 급격한 전이가 발생합니다. 물론 '0'에서 '1'로의 전이에서는 그 반대가 발생합니다. 이 급격한 전압 변화는 신호를 전달하는 물리적 매체에 의해 왜곡됩니다. 케이블과 PCB traces는 low-pass filter처럼 작동합니다.

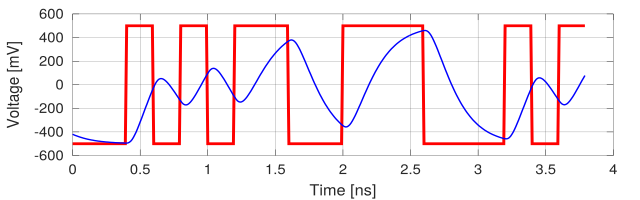

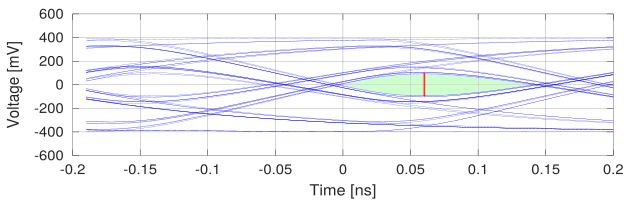

이 이미지는 위의 waveforms 예와 동일하지만 더 어려운 물리적 채널의 시뮬레이션을 보여줍니다.

파란색 waveform은 수신기에 도착하는 전압이 이전에 전송된 몇 개의 bits 값을 "기억"하는 방식을 보여줍니다. 수신기는 전압이 음수인지 양수인지에 따라 '0' 또는 '1'를 결정해야 한다는 점을 상기해 보세요. 따라서 이전 bits 의 값이 수신기의 결정을 방해합니다. 한 bit의 값이 다른 bit 에 대한 수신기의 결정을 방해한다는 사실을 Inter-Symbol Interference (ISI)라고 합니다.

동일한 물리적 채널 시뮬레이션을 위한 eye diagram :

이 eye diagram은 여전히 '0'와 '1'의 차이를 알 수 있음을 보여주지만, 마진이 훨씬 작습니다. 다시 말해, 오류를 발생시키는 데 필요한 노이즈가 훨씬 적습니다.

위의 eye diagram 에서 시뮬레이션된 효과 외에도 신호는 다른 방식으로도 왜곡됩니다.

- 신호는 수신기로 전송되는 동안 에너지를 잃으므로 차동선 사이의 전압은 전송되는 전압보다 낮아집니다.

- 신호가 송신기에서 수신기로 이동할 때 반사가 추가됩니다. 이 효과는 음향 에코와 유사하며, 특히 신호가 커넥터나 다른 종류의 전도 매체의 갑작스러운 불연속성을 통과할 때 발생합니다.

- 다양한 외부 소스의 신호에 노이즈가 추가됩니다. 이는 일반적으로 MGTs간 통신에서 지배적인 요소가 아니며, 왜곡의 영향이 일반적으로 더 큽니다. 그러나 노이즈는 길고 제대로 분리되지 않은 케이블에서는 상당할 수 있습니다.

이제 물리적 채널의 신호 왜곡을 완화하기 위한 두 가지 메커니즘을 살펴보겠습니다. 수신기의 일부인 equalizer와 송신기의 일부인 pre-emphasis입니다.

Equalizer

equalizer는 MGT에 도착하는 아날로그 신호를 조작합니다. 이 장치의 목적은 물리적 채널의 신호 왜곡 효과를 완화하는 것입니다. 이를 통해 equalizer는 채널의 비트 오류 확률을 줄이고 더 높은 데이터 속도를 허용합니다. equalizer는 항상 Rx PMA처리 체인의 첫 번째 단계입니다.

주로 두 가지 종류의 equalizers가 사용됩니다. MGT는 둘 다 지원할 수 있습니다.

- LPM (Low Power Mode). 이 equalizer는 일반적으로 아날로그 신호 스펙트럼의 상위 부분을 감쇠시키는 물리적 채널의 경향을 보상하는 high-pass filter 로 구성됩니다. 일부 MGTs는 이 filter를 수신 신호에 자동으로 적응시킵니다. 덜 진보된 MGTs의 경우 application logic은 여러 가능성 중에서 하나의 filter를 선택해야 합니다.

- DFE (Decision Feedback Equalizer)에 대한 자세한 설명은 아래에 있습니다.

위의 예에서 Rx PMA는 0.2 ns의 시간 주기마다 두 개의 input pins (D+ 와 D-) ) 사이의 전압을 측정합니다. 이 전압이 음수인지 양수인지에 따라 Rx PMA는 '0' 또는 '1'를 감지합니다. equalizer가 사용되면 Rx PMA는 대신 equalizer 의 output 에 의존합니다.

DFE를 사용하는 경우, 송신기가 전송된 bits가 서로 통계적으로 독립적임을 보장한다고 가정합니다. 물리적 채널이 신호를 왜곡하지 않는다면 어떨까요? 이 경우, Rx PMA가 '0' 또는 '1'를 결정하는 데 사용하는 전압도 서로 통계적으로 독립적입니다. 즉, Rx PMA가 analog input signal을 검사할 때마다 이전 signals 나 미래의 signals와 통계적 관계가 없어야 합니다.

하지만 실제로는 물리적 채널이 데이터 스트림을 전달하는 신호를 왜곡합니다. 따라서 '0' 또는 '1'를 나타내는 전압 사이에는 통계적 관계가 있습니다. low-pass filter 효과는 전압 신호를 흐리고 반사("에코")도 신호 품질을 떨어뜨립니다. 각 bit의 전압 레벨은 인접한 bits로 넘칩니다. 위에서 언급했듯이 이 효과는 Inter-Symbol Interference (ISI)라고 합니다. 수신기가 ISI의 효과를 완화하기 위해 아무것도 하지 않으면 bits 간의 이 상호 간섭은 채널에 노이즈를 추가하는 것과 같습니다.

DFE는 echo canceler와 유사하게 작동합니다. 이는 '0' 또는 '1'를 나타내는 samples 사이의 모든 correlation을 제거하기 위해 자체적으로 조정되는 filter 로 구성됩니다. 더 정확하게는 감지된 bits ('0' 또는 '1')와 이웃하는 bits에 속하는 아날로그 신호 간의 상관 관계를 제거합니다. 다시 말해, DFE가 목표를 달성했다면 bit의 값을 결정하는 데 사용되는 아날로그 신호와 다른 bit의 값 간에 통계적 상관 관계가 없습니다. 이 경우 ISI은 0으로 줄어들며, 이는 채널의 번짐 효과와 반사가 전송 품질에 영향을 미치지 않는다는 것을 의미합니다.

채널에서 전송되는 bits 간에 통계적 상관 관계가 있는 경우 DFE는 이 상관 관계를 제거하려고 시도합니다. 결과적으로 DFE는 아날로그 신호의 물리적 채널 왜곡에 해당하지 않는 방식으로 아날로그 filter를 조정합니다. 따라서 DFE는 신호를 복구하는 대신 왜곡합니다. 이것이 DFE가 활성화될 때 항상 scrambler가 필요한 이유입니다.

전송된 bits가 서로 상관이 없는지 확인할 방법이 없다면 LPM equalizer가 적합할 수 있습니다. MGT의 datasheet은 일반적으로 LPM equalizer를 scrambler없이 사용할 수 있는지 여부를 나타냅니다.

모든 MGTs 에 DFE가 있는 것은 아니지만, 거의 모든 MGTs 에 어떤 종류의 LPM equalizer가 있습니다. datasheets 의 정보는 MGT가 어떤 종류의 equalizers를 지원하는지, 그리고 이 equalizers가 어떻게 작동하는지에 대한 정보가 종종 불완전합니다. datasheet이 equalizer의 유형에 대해 아무것도 말하지 않는다면, 그것은 아마도 LPM일 것입니다.

DFE는 equalizer의 고급형이지만, bits 계열 제품들이 서로 상관관계가 없더라도 LPM보다 항상 성능이 더 좋은 것은 아닙니다 . 특히 물리 채널의 품질이 비교적 높은 경우에는 LPM가 DFE보다 더 나은 성능을 보일 수 있습니다.

Pre-emphasis

수신기에 도착하는 신호를 개선하는 방식으로 송신기의 output signal을 조작하는 것이 도움이 될 수 있습니다. 이 방법은 pre-emphasis라고 하며, 특히 신호의 왜곡이 너무 심해서 수신기가 데이터 스트림에서 전혀 동기화할 수 없는 경우에 유용합니다. 이 방법에는 여러 가지 변형이 있으며, 각 MGT 에는 고유한 기능 세트가 있습니다.

대부분의 상황에서 물리적 채널은 low-pass filter의 효과를 갖습니다. 송신기는 송신기의 output signal을 형성하여 채널의 왜곡 중 일부를 사전에 보상할 수 있습니다. 가장 간단한 메커니즘은 post-cursor emphasis입니다. 물리적 채널이 송신기의 output의 변화에 느리게 반응하기 때문에 송신기는 bit이 변경될 때 더 높은 전압을 적용하여 이를 보상합니다. 또는 더 정확하게 말해서 송신기는 bit이 변경되지 않을 때 전압을 줄입니다.

이 메커니즘을 보여주기 위해 위의 예에서 송신기의 output은 -500 mV 또는 500 mV (즉, '0' 또는 '1')였음을 기억하세요.

post-cursor emphasis의 경우 output이 '0'에서 '1'로 변경되면 송신기의 output은 이전과 마찬가지로 500 mV가 됩니다. 하지만 다음 bit이 다시 '1'이면 출력 전압이 낮아집니다(예: 400 mV). '1'에서 '0'로 전환하는 경우에도 동일한 일이 발생합니다. 이 경우 출력 전압은 -500 mV가 됩니다. 하지만 다음 bit이 다시 '0'이면 전압은 -400 mV가 됩니다.

이 이미지는 waveforms를 적용한 마지막 이미지와 동일한 시뮬레이션을 보여주지만 post-cursor emphasis가 적용되었습니다.

빨간색 waveform은 post-cursor emphasis 의 작동 방식을 보여줍니다. 출력 전압은 bit이 변경될 때마다 약간씩 증가하고, 그렇지 않으면 더 낮은 전압으로 돌아갑니다. 이 방법은 종종 de-emphasis라고 불리는데, 송신기가 반복되는 bits의 전압을 감소시키기 때문에 이러한 bits는 "덜 강조"됩니다.

파란색 waveform을 위의 이미지와 비교하면 이 전압의 스윙이 더 작다는 것이 분명합니다. 이는 큰 문제가 아닌 것처럼 보일 수 있지만, eye diagram에서 차이가 더 분명합니다.

이것은 분명히 더 나았지만 충분하지는 않습니다. 이런 시나리오에서는 여전히 equalizer가 필요합니다.

post-cursor emphasis는 간단한 FIR filter로 설명할 수 있습니다. emphasis가 없는 송신기의 전압을 x(n) 로 표시합니다(n은 전송되는 bit 의 번호입니다). 각 x(n)은 -500 mV 또는 500 mV값을 가질 수 있습니다. 따라서 post-cursor emphasis가 있는 송신기의 output은 다음과 같이 쓸 수 있습니다.

y(n) = 0.9 x(n) - 0.1 x(n-1)

이것은 고주파 신호를 선호하는 FIR filter를 위한 간단한 expression 입니다. 이는 low-pass filter로서의 물리적 채널 동작에 대한 보상으로 볼 수 있습니다.

"post-cursor emphasis" 표현의 "post-cursor" 부분은 해당 FIR filter가 다음과 같이 작성될 수 있다는 사실과 관련이 있습니다.

y(n) = (1-a) x(n) - a x(n-1)

이 expression에서 a는 보통 양수로 선택됩니다.

이 FIR filter는 기본적으로 다음과 같이 말합니다. y(n) 의 값은 대부분 x(n)에 따라 달라지지만, x(n-1)이 같은 값을 가졌다면 y(n)은 0에 조금 더 가깝습니다. y(n)의 조작은 이전 bit에 따라 달라집니다.

따라서 "cursor"라는 단어는 현재 전송된 bit와 관련이 있습니다. "post"라는 단어는 이 filter가 이전에 전송된 bit, 즉 "cursor" 뒤의 bit 에 의존한다는 사실을 나타냅니다.

고주파 신호에 더 유리한 FIR filter 의 아이디어를 일반화하는 것이 가능합니다. 특히, 이 FIR는 종종 MGTs에서 구현됩니다.

y(n) = apre x(n+1) + a0 x(n) - apost x(n-1)

이 expression에서 apost는 이미 제시된 post-cursor emphasis 와 관련이 있습니다. apre는 "cursor" 이전의 bit 에 대한 종속성을 나타냅니다. 즉, pre-cursor emphasis가 며 때로는 preshoot라고도 합니다. 이것은 FIR filter로 표현할 수 있는 송신기의 output signal 조작의 전체 범위를 포괄하는 용어인 pre-emphasis와 혼동되어서는 안 됩니다.

각 MGT는 전송된 신호를 형성하는 데 다양한 가능성을 제공합니다. post-cursor emphasis는 일반적으로 여러 protocols 에 필요하기 때문에 사용할 수 있습니다. 다른 변형의 경우 MGT에 따라 달라집니다.

pre-emphasis 의 명백한 단점은 송신기 조정 결과가 수신기에서만 볼 수 있다는 것입니다. equalizer는 최적의 수신을 달성하기 위해 지속적으로 스스로를 조정할 수 있다는 점을 기억하세요. 하지만 일반적으로 pre-emphasis 메커니즘은 다른 쪽에서 신호가 얼마나 잘 수신되는지 알지 못합니다. 이 문제는 protocol로 해결할 수 있습니다. 예를 들어, Displayport protocol은 수신 측이 송신기에 요청을 보낼 수 있는 메커니즘을 지정합니다. 이런 식으로 수신기는 송신기의 전압 레벨과 post-cursor emphasis의 레벨을 제어합니다.

Pre-emphasis는 physical channel이 미리 알려져 있는 경우에도 유용합니다. 예를 들어 두 개의 FPGAs가 PCB에서 서로 연결되어 있는 경우입니다. 그럼에도 불구하고 채널의 매개변수가 알려지지 않은 경우에도 pre-emphasis를 사용하는 것이 좋은 생각일 수 있으며, 특히 높은 데이터 속도(8 Gb/s 이상)의 경우 더욱 그렇습니다.

pre-emphasis 메커니즘과 equalizer는 서로 대체할 수 없다는 점에 유의하세요. 둘 다 신호 품질을 개선하고 오류를 줄이는 filters 입니다. equalizer는 일반적으로 이 두 가지 중에서 더 강력한 도구입니다. pre-emphasis의 역할은 equalizer를 돕거나 수신기가 송신기와 동기화할 수 있을 만큼 신호 품질이 충분히 좋은지 확인하는 것입니다.

Pre-emphasis는 많은 애플리케이션에서 전혀 사용되지 않습니다. 이 도구는 특히 두 MGTs 사이의 거리가 길 때, 특히 신호가 PCB로 이동할 때 유용합니다. 거리가 상당히 짧고 수신기에 좋은 equalizer가 장착되어 있는 경우 일반적으로 송신기의 output signal을 조작할 이유가 없습니다.

Statistical eye scan

모든 데이터가 오류 없이 도착하더라도 채널의 품질을 평가하는 것이 종종 필요합니다. 특히 채널이 오류를 생성하기 시작하는 데 얼마나 남았는지 아는 것이 흥미롭습니다. 채널이 견고한지, 아니면 물리적 미디어에 가장 작은 변화가 발생하면 오류가 시작될까요?

또한, 이전 페이지 에서 언급했듯이, 채널이 유용한 데이터 전송에 사용될 때는 BER 테스트가 동시에 수행될 수 없습니다. 따라서 채널이 사용되는 동안 채널의 품질을 평가하기 어렵습니다(예: xillyp2p 와 같이 모든 오류를 보고하는 일부 protocols 제외).

링크의 품질을 평가하는 일반적인 방법은 수신기에서 eye diagram을 측정하는 것입니다. 이는 신호가 케이블과 커넥터와 함께 도착할 때 수행할 수 있습니다. 이 목적을 위한 측정 장비가 있습니다(꽤 비쌉니다). 그러나 신호가 PCB를 타고 chip (특히 FPGA )에 도착하면 일반적으로 신호를 수집할 곳이 없습니다. probe를 사용하여 PCB 의 전선을 만지면 신호 모양이 극적으로 바뀌므로 측정이 무의미해집니다.

이 문제에 대한 우아한 해결책은 statistical eye scan입니다. 즉, Rx PMA 자체가 signal의 eye diagram을 측정한다는 의미입니다. 이 방법에는 여러 가지 장점이 있습니다.

- signal은 Rx PMA가 '0' 또는 '1'로 결정되는 지점에서 정확히 측정되었습니다.

- 측정 결과는 signal에 영향을 미치지 않습니다.

- 측정에는 equalizer의 보정이 포함됩니다. 따라서 어떤 equalizer를 사용할지 선택하고 parameters를 미세 조정하는 데 도움이 됩니다.

- CDR가 송신기의 clock의 jitter 에 대처할 수 없다면 이는 이 측정에서 확인할 수 있습니다.

- 측정은 Rx PMA의 정상적인 작동을 방해하지 않습니다. 따라서 실제 데이터를 전송하는 데 사용되는 동안 채널을 테스트할 수 있습니다.

이 방법에는 단 하나의 단점이 있습니다. 그 결과는 실제로 eye diagram이 아닙니다. 하지만 그 결과는 거의 똑같이 유용합니다.

위에서 Rx PMA는 수신 신호가 '0'인지 '1'인지 도착 신호의 차동 전압이 음수인지 양수인지에 따라 결정한다는 것을 기억하세요. CDR는 최적의 타이밍으로 이 결정을 내리는 역할을 합니다.

statistical eye scan의 경우, '0' 또는 '1'에 대한 결정을 내리는 추가 장치가 있습니다. 그러나 이 두 번째 장치는 첫 번째 장치보다 약간 일찍 또는 약간 늦게 결정을 내립니다. 이 시간 오프셋은 MGT의 registers를 설정하여 제어합니다(이는 MGT가 작동하는 동안 수행할 수 있음).

두 장치 간의 또 다른 차이점은 신호가 '0'인지 '1'인지 판별하는 방법입니다. 이미 언급했듯이, 첫 번째 유닛은 신호의 전압을 0과 비교합니다. 두 번째 유닛은 대신 다른 전압 임계값 범위와 비교할 수 있습니다. 예를 들어, 전압 임계값이 100 mV로 선택된 경우 두 번째 유닛은 수신 신호가 100 mV보다 높으면 '1'를 결정합니다. 그렇지 않으면 '0'를 결정합니다.

따라서 두 번째 유닛은 첫 번째 유닛과 정확히 동일한 작업을 수행하지만 시간과 전압에 오프셋이 있습니다. MGT 내부의 logic은 지정된 수의 결정을 자동으로 비교하고 결정이 달랐던 횟수를 계산합니다. 다시 말해, 이 logic은 타이밍과 임계 전압이 이동했다면 bit 에서 Rx PMA의 결정이 몇 번 달랐을지 계산합니다.

이 두 단위의 결정 사이에 차이가 전혀 없다면, 두 번째 단위의 위치(시간과 전압으로 표시)가 위의 eye diagrams 에서 녹색으로 표시된 영역 내부에 있다는 것을 의미합니다. 이 상황은 상당한 기간의 측정 후 0의 카운트 결과로 인식됩니다. 두 번째 단위의 위치가 녹색 영역의 가장자리에 접근함에 따라 카운터의 결과는 점점 더 높아집니다.

statistical eye scan은 시간 오프셋과 전압 임계값의 범위로 두 장치 간의 이러한 비교를 반복하여 얻습니다. 이는 application logic 에 의해 수행되거나 MGT의 registers를 JTAG로 설정하여 수행됩니다. 이 프로세스는 임계 전압의 범위에 대해 for-loop 내부의 시간 오프셋 범위에 대해 for-loop을 실행하는 컴퓨터 프로그램과 유사합니다. 이 작업을 완료하는 데 걸리는 시간은 측정의 정확도에 따라 달라집니다.

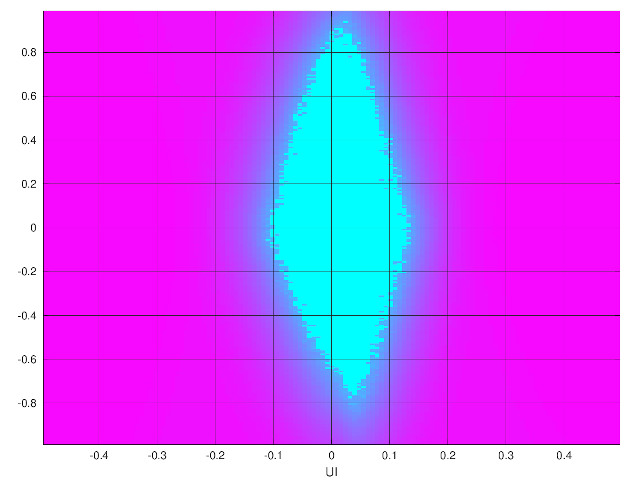

이는 Artix-7 FPGA를 사용하여 얻은 statistical eye scan 의 예시입니다( 다른 페이지 에서 가져온 것입니다). 가운데 녹색 영역은 위의 eye diagrams 의 녹색 영역에 해당합니다. 위의 예시에서는 한 가지 유형의 신호 왜곡만 시뮬레이션했기 때문에 측정 결과는 위의 모든 이미지와 정량적으로 다릅니다.

이런 이미지를 얻는 데는 약 1분이 걸립니다. 하지만 1초도 안 걸려 얻을 수 있는 더 조잡한 이미지를 기반으로 채널의 품질을 잘 평가할 수 있습니다.

statistical eye scan을 얻기 위해 일반적으로 아무것도 설계할 필요가 없습니다. 특히, 이 프로세스는 JTAG 연결의 도움으로 Vivado 에서 수행할 수 있습니다. 안타깝게도 모든 MGTs가 statistical eye scan의 기능을 갖추고 있는 것은 아닙니다.

이것으로 MGTs에 대한 이 시리즈 의 다섯 번째 페이지를 마무리합니다. 다음 페이지에서는 PMA 와 일반 데이터 스트림이 꺼졌을 때의 기능에 대해 계속 설명합니다.