이 페이지는 Multi-Gigabit Transceiver (MGT)를 소개하는 일련의 페이지 중 첫 번째이며, 이 시리즈의 향후 내용에 대한 개요를 제공합니다.

소개

Multi-Gigabit transceivers (MGTs)는 컴퓨터 또는 전자 시스템 내부의 여러 부분 간의 통신에서 중요한 역할을 합니다. 컴퓨터 내부의 여러 잘 알려진 인터페이스는 MGTs를 기반으로 합니다(예: PCIe 및 SATA). 다른 잘 알려진 인터페이스는 컴퓨터와 주변 장치 간의 통신에 사용됩니다(예: Gigabit Ethernet, SuperSpeed USB, Thunderbolt 및 Displayport).

MGTs는 전자 부품 간, 예를 들어 두 개의 FPGAs간 연결에도 사용됩니다. 이 경우, 통신은 잘 알려지지 않은 protocols 나 비표준 protocol을 기반으로 하는 경우가 많습니다. 하지만 FPGA를 다른 유형의 부품과 연결하거나, Xillyp2p 와 같이 다른 부품끼리 연결하는 데 MGTs를 사용할 수도 있습니다.

예를 들어, 광섬유 트랜시버는 이 예시 설계 에서 볼 수 있듯이 MGTs와 직접 연결되는 표준 모듈(특히 SFP+ 폼 팩터)인 경우가 많습니다. 일부 고속 ADC/DACs는 sample data (일반적으로 JESD204 protocol기반)를 전송하기 위해 MGTs를 사용하기도 합니다. 일부 protocols는 비디오 데이터 전송용으로 설계되었습니다(예: 일부 MIPI의 protocols는 물리 계층용).

MGTs는 종종 양방향 protocols에 사용되지만 각 MGT는 실제로 두 개의 독립적인 부분으로 구성됩니다. 송신기와 수신기. 따라서 두 부분 중 하나를 끄면 단방향 전송에 MGT를 사용할 수 있습니다. 대부분의 FPGA MGTs에서는 송신기와 수신기의 parameters를 독립적으로 구성할 수도 있습니다.

요약하자면, MGTs는 많은 애플리케이션에서 사용됩니다. 종종 인터페이스의 이름은 MGTs가 사용된다는 것을 의미하지 않지만(예: Gigabit Ethernet, SATA 및 DisplayPort), 물리 계층은 MGTs로 구성됩니다.

Xilinx (그리고 AMD)가 MGTs를 다른 이름으로 부른다는 점도 언급할 가치가 있습니다. RocketIO, GTX, GTH, GTY, GTP, GTM등. 각 이름은 트랜시버의 특정 하드웨어 구현을 나타내므로 이 이름은 트랜시버가 가진 데이터 전송 속도와 기타 성능 속성에 대한 정보를 알려줍니다.

이 페이지 시리즈에서는 MGTs 의 기본 사항과 이와 관련하여 일반적으로 사용되는 몇 가지 기술 용어를 설명합니다. 이 페이지의 목적은 기술 문서를 더 쉽게 읽을 수 있도록 하는 것이며, 특히 어떤 매개변수가 프로젝트에 관련이 있고 어떤 매개변수가 관련이 없는지 인식할 수 있도록 하는 것입니다.

MGT는 무엇인가요?

모든 복잡한 기능 뒤에는 MGT가 단지 SERDES일 뿐이라는 사실을 깨닫는 것이 중요합니다. 데이터를 수신하고 전송하는 전자 빌딩 블록입니다. MGT의 물리적 세계와의 전기적 인터페이스는 차동 쌍을 구성하는 두 개의 와이어로 구성됩니다. 첫 번째 와이어("플러스" 또는 "포지티브" 와이어)의 전압이 다른 와이어("마이너스" 또는 "네거티브" 와이어)의 전압보다 높으면 물리적 상태는 '1'에 해당합니다. 그렇지 않으면 '0'입니다. 이는 LVDS와 같은 차동 인터페이스와 동일한 원리입니다.

SERDES 와 또 다른 유사점은 MGT와 application logic 의 인터페이스가 병렬 단어로 구성되어 있다는 것입니다. application logic의 clock의 각 사이클마다 여러 개의 bits가 application logic 와 MGT사이에 전송됩니다. 이러한 배열은 데이터 속도가 FPGA에 가능한 최대 clock frequency 보다 훨씬 높기 때문에 필요합니다.

그러나 일반적인 SERDES 와 MGT사이에는 몇 가지 중요한 차이점이 있습니다. 다음은 그 중 일부입니다.

- MGTs는 일반 SERDES보다 훨씬 높은 데이터 전송 속도를 처리할 수 있습니다.

- SERDES 의 수신기는 데이터 스트림과 함께 송신기의 clock을 제공받아야 합니다. 반면 MGT 수신기는 데이터 스트림의 signal 에만 의존할 수 있습니다. MGT는 데이터 스트림의 signal 와 일치하는 clock을 생성하고 대신 이 clock을 사용합니다. 이 기능을 clock data recovery, CDR 라고 합니다. MGT 수신기가 송신기의 clock에 액세스할 수 있더라도 reference clock로만 사용되고 data clock 자체로는 사용되지 않습니다.

- Bit errors는 MGT를 사용하는 데이터 링크에서 허용되며 정상적인 현상입니다. BER는 일반적으로 10-12 또는 10-15미만에서 발생할 것으로 예상됩니다. 일반적인 SERDES에서 bit error가 발생하면 오작동으로 간주되지만, MGT의 경우에는 그렇지 않습니다.

- MGT를 사용할 경우, 전선 쌍에서 전송되는 데이터 스트림의 내용에 제한이 있습니다. 데이터 스트림은 항상 DC 밸런스가 필요합니다. 즉, 데이터 스트림의 '0'와 '1'의 수는 평균적으로 동일해야 합니다. 또한, 전송되는 bits가 서로 통계적으로 독립적이어야 하는 경우가 많습니다. 이에 대한 자세한 내용은 아래를 참조하세요.

- MGT는 out-of-band signals (OOBs)를 생성하고 감지할 수 있습니다. 이러한 signals는 에너지를 절약하기 위해 일반 데이터 흐름이 중단될 때 전송됩니다. 이러한 signals 의 목적은 주로 data bits전송을 재개하기 위해 다른 쪽 수신기를 깨우는 것입니다.

그렇다면 MGT가 왜 그렇게 복잡한 것일까요?

FPGA 프로젝트를 위해 MGT 블록을 구성하려고 시도한 사람이라면 누구나 매개변수와 선택 사항이 많다는 것을 알고 있을 것입니다. 왜 이런 식이어야 합니까?

사실, 복잡할 필요는 없습니다. 이 예시 설계 에서 보여지듯이 MGT를 SERDES처럼 사용하면 복잡성이 대부분 제거됩니다.

하지만 MGT를 사용하는 것은 일반적으로 복잡하며, 그 이유는 주로 세 가지입니다. 첫째, MGT 블록은 logic fabric에서 구현할 수 있지만 효율성을 위해 MGT 의 일부로 구현되는 많은 빌딩 블록을 구현하기 때문입니다. 예를 들어, 모든 MGTs는 8b/10b를 인코딩하고 디코딩할 수 있는 기능이 있지만 이 작업은 application logic에서 수행할 수 있습니다. 하지만 이 인코딩 기술은 매우 일반적으로 사용되므로 MGT는 대신 처리할 수 있는 기능이 있습니다.

두 번째 이유는 clocking 와 관련이 있습니다. MGT의 적절한 작동을 위해서는 여러 개의 clocks가 필요합니다. 상황을 더욱 복잡하게 만드는 것은 clock의 품질(특히jitter )에 대한 요구 사항이 FPGA의 logic fabric에 사용된 clocks 와 비교할 때 더 엄격하다는 것입니다. 그리고 때로는 SSC (Spread Spectrum Clocking)도 사용되어 상황을 더욱 복잡하게 만듭니다.

따라서 clocking을 제대로 만드는 것은 때로는 MGT 에 대한 올바른 매개변수를 선택하는 것보다 더 어렵습니다.

세 번째 이유는 MGTs가 여러 표준 통신 protocols를 지원하도록 설계되었다는 것입니다. 따라서 특정 protocol 에 필요한 기능의 이름은 종종 protocol의 사양에서 가져옵니다. 이러한 전문 용어는 관련 protocol을 모르는 사람에게는 아무 의미가 없습니다. 이로 인해 FPGA에 대한 MGT 블록을 설정할 때 어떤 기능을 활성화할지 결정하기 어렵습니다.

이 모든 주제에 대해서는 이 시리즈의 나머지 페이지에서 더 자세히 설명합니다.

알아두어야 할 사항

대부분의 사용 사례에서 MGTs는 다른 잘 확립된 protocol, 특히 PCIe의 물리적 계층으로 사용됩니다. 이러한 상황에서 FPGA tools는 세부 사항을 처리하며, 하위 수준에서 무슨 일이 일어나는지 많이 이해할 필요가 없습니다.

하지만 application logic을 MGT에 직접 연결하려는 경우 이 logic이 해결해야 할 몇 가지 과제를 알고 있어야 합니다. 이러한 문제 중 일부는 FPGAs사이에서 사용하도록 의도된protocols 에서 처리합니다.

이것은 고려해야 할 주제의 짧은 목록입니다. 이러한 주제 각각은 이 시리즈의 나머지 페이지에서 더 자세히 논의됩니다.

- 단어 정렬: 모든 SERDES와 마찬가지로 MGT는 바이트 또는 더 큰 단어가 시작되는 위치에 대한 사전 지식이 없습니다. SERDES의 경우 이 문제는 일반적으로 도착하는 데이터 스트림이 의미가 있을 때까지 한 번에 하나의 bit (bit slipping)씩 병렬 단어를 이동하려고 시도하여 해결됩니다. MGTs를 기반으로 하는 Protocols는 일반적으로 이 목적을 위해 동기화 단어에 의존합니다.

- 물리적 와이어의 bits는 DC 밸런스여야 합니다. 가장 쉬운 해결책은 8b/10b 인코딩을 사용하는 것이지만, 다른 가능성이 있고 때로는 더 적합한 가능성도 있습니다.

- Scrambling: 수신 MGT에 equalizer를 사용하는 것은 거의 항상 좋은 생각입니다. equalizer는 물리적 미디어의 불완전성을 보상하고, 그렇게 함으로써 BER를 줄입니다. 이는 특히 데이터 속도가 높을 때, 저렴한 케이블이 사용될 때 또는 물리적 거리가 길 때 그렇습니다. 그러나 일부 유형의 equalizers는 전송된 데이터가 통계적으로 무작위적이어야 합니다. 전송된 데이터 스트림에서 한 bit 와 다른 bit 간의 상관 관계는 허용되지 않습니다. 일반적인 해결책은 페이로드 데이터와 bits의 의사 난수 시퀀스 사이에서 XOR을 수행하는 scrambler를 사용하는 것입니다. 수신기는 동일한 의사 난수 시퀀스로 XOR을 수행하고 이런 방식으로 원래 데이터 스트림을 얻습니다.

- Bit errors: 데이터는 수신 MGT에 오류와 함께 도착할 수 있습니다. 이 데이터를 소비하는 logic은 이러한 오류에 대처하도록 설계되어야 합니다. 일부 애플리케이션에서는 오류가 무시할 만큼 드물다고 간주됩니다(예: 원시 비디오 데이터를 전송할 때 BER가 10-15아래에 있는 경우). 다른 애플리케이션에서는 데이터 링크가 안정적임을 보장하기 위해 오류 감지 및/또는 재전송 메커니즘이 필요합니다.

- clock frequencies의 차이점: MGT가 데이터 스트림을 수신하면, 이 signal은 다른 쪽의 clock (즉, 송신기의 clock)를 기반으로 합니다. 이 clock은 수신기 쪽에서 사용 가능한 clock 와 비교하여 약간 다른 frequency를 가질 수 있습니다. 그러나 MGT 와 application logic 간의 인터페이스는 종종 로컬 clock을 기반으로 합니다. 따라서 송신기의 clock이 수신기의 clock보다 빠르면 MGT가 이 데이터를 application logic에 전달할 수 있는 것보다 더 빨리 데이터를 수신한다는 것을 의미합니다. 결과적으로 이 과도한 데이터는 MGT 블록 내부에 축적되고 결국 어떤 종류의 overflow가 발생합니다. 반대로 도착하는 데이터 속도가 로컬 clock보다 낮으면 MGT는 각 clock cycle에서 데이터를 전달할 수 없습니다. 이러한 문제는 reference clock이 데이터 스트림과 함께 송신기에서 수신기로 전달되는 경우에도 발생합니다. clock의 frequency 에서 약간의 변동이 있어도 이런 종류의 문제가 발생하기에 충분합니다. protocol은 보통 idle words의 도움으로 이 문제를 해결합니다.

- 에너지 소비량: MGTs는 많은 전력을 소모하는 경향이 있습니다. 이는 부분적으로 높은 데이터 전송 속도 때문이며, 종종 고품질 PLLs는 많은 에너지를 낭비하는 것으로 나타났습니다. 따라서 MGT는 사용하지 않을 때, 심지어 아주 짧은 기간이라도 종료하는 것이 바람직합니다. 예를 들어, SuperSpeed USB 링크는 50μs만큼 짧은 기간 동안 데이터가 전송되지 않으면 종종 데이터 스트림을 끕니다. 그런 다음 OOB handshake는 필요할 때 작동을 재개하는 데 사용됩니다.

PMA, PCS 및 clocking

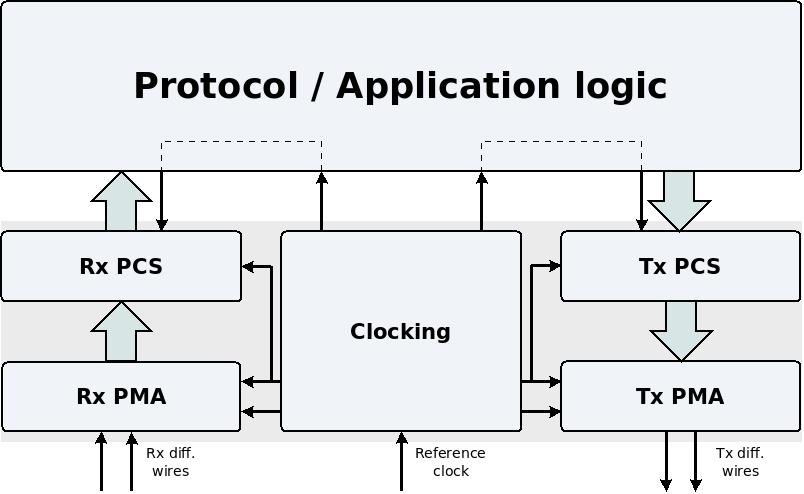

이 블록 다이어그램은 MGT 의 구성 요소와 application logic와의 상호 작용을 보여줍니다.

MGT 의 기능은 일반적으로 세 부분으로 나뉩니다.

- Clocking : 위에서 언급했듯이, MGT의 작동에는 여러 개의 clocks가 필요합니다. FPGA tools가 이러한 clocks의 매개변수를 자동으로 구성하더라도 이러한 clocks가 어떻게 생성되는지 알고 있어야 합니다.

- PMA (Physical Medium Attachment): 이 부분에는 MGT의 SERDES 와 아날로그 신호 서브시스템(OOB signals, receiver detection, equalizer, pre-emphasis 등)이 포함됩니다. 이 부분에는 CDR도 구현됩니다.

- PCS (Physical Coding Sublayer): 이 부분에는 protocol통신을 구현하는 데 도움이 될 수 있는 logic이 포함되어 있습니다. 인코더 및 디코더, 단어 정렬, gearboxes, FIFOs등. PCS 의 대부분 기능은 대신 logic fabric 에서 구현할 수 있지만 단순성과 효율성을 위해 MGT 내부에 구현됩니다.

이 주제는 이 페이지 시리즈 에서 더 자세히 논의됩니다.

PIPE 인터페이스

PIPE 표준은 언급할 가치가 있습니다. 이 표준은 PCIe, SuperSpeed USB 또는 SATA를 구현하는 MGT 와 logic 간의 연결을 정의합니다. 여기에는 데이터, 제어 신호 및 상태 신호를 통신하는 데 사용되는 ports가 포함됩니다.

이 표준에서 MGT는 PHY 계층이라고 하며, protocol은 MAC 계층이라고 합니다. 이 용어는 Ethernet, USB 1.x 및 USB 2.0을 정의하는 표준에서도 사용됩니다. 이러한 표준은 일반적으로 두 개의 별도 chips에 의해 구현됩니다. 예를 들어, processor chip에서 Ethernet를 구현하려면 MAC 계층이 이 chip에 구현되고 PHY 계층은 별도의 chip에 구현됩니다. PIPE 표준은 PCIe, SuperSpeed USB 또는 SATA가 실제로 항상 동일한 chip에 완전히 구현되더라도 동일한 정신으로 작성됩니다. PIPE 표준에서 정의하는 MAC 계층과 PHY 계층 간의 연결은 chip내부에서 이루어지며 외부에서는 거의 볼 수 없습니다.

PIPE 표준의 중요한 영향은 괜찮은 FPGA MGT가 항상 PCIe에 필요한 PIPE 인터페이스를 구현한다는 것입니다. SATA 에 대한 PIPE 인터페이스도 종종 지원됩니다. 이는 이 두 가지 protocols를 구현할 때 분명히 유용하지만, 또 다른 중요한 이점이 있습니다. 다양한 FPGAs는 MGT와 유사한 인터페이스를 가지고 있습니다. 특히, 거의 모든 MGTs에서 찾을 수 있는 몇 가지 기능적 요소가 있습니다.

결론

이 페이지에서는 MGT 와 그 복잡성에 대한 개요를 제시했습니다. 이 시리즈의 나머지 페이지에서는 위에서 언급한 많은 개념이 설명됩니다. 하지만 그 전에 두 개의 FPGA MGTs를 연결할 때 자주 사용되는 protocols 에 대한 간략한 개요부터 시작하겠습니다 .