소개

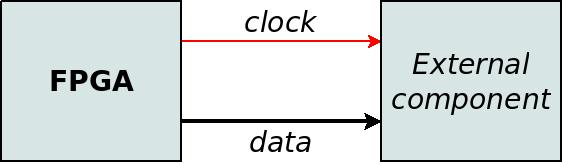

이 페이지에서는 source-synchronous data outputs에 대해 설명합니다. 이 기술은 data outputs가 FPGA가 이러한 outputs와 병렬로 생성하는 clock 와 동기화됨을 의미합니다.

이 접근 방식은 외부 구성 요소와의 인터페이스가 FPGA에서 output ports 로만 구성된 경우 확실한 선택입니다. 이 페이지 하단에 설명된 대로 I/O가 양방향인 경우에도 적합합니다. 일반적으로 clock 와 data 사이의 관계를 설명하는 별도의 페이지 도 있습니다.

기본 애플리케이션

이 Verilog 예를 고려하십시오.

module top (

input clk,

output reg [7:0] data_out,

output reg sync_clk_out

);

always @(posedge clk)

begin

sync_clk_out <= !sync_clk_out;

if (sync_clk_out)

data_out <= data_out + 1;

end

endmodule

@data_out는 @sync_clk_out의 falling edge와 동시에 값을 변경합니다. @sync_clk_out가 낮을 때 @data_out는 변경되지 않습니다. @sync_clk_out가 높을 때 @data_out는 @clk의 rising edge에 대응하여 새로운 값으로 변경됩니다.

IOB registers가 @data_out 와 @sync_clk_out둘 다에 사용된다면, 이 모든 output signals는 실질적으로 동시에 값을 변경합니다. 따라서 이 signals를 수신하는 외부 구성 요소는 @sync_clk_out를 clock로 사용할 수 있습니다. 이런 방식으로 외부 구성 요소의 timing 요구 사항을 충족하는 것은 일반적으로 쉽습니다( @data_out 의 sampling이 @sync_clk_out의 rising edge와 동기화된다고 가정).

DDR registers사용

위의 예에는 중요한 단점이 있습니다. @sync_clk_out 의 frequency는 @clk의 frequency 의 절반입니다. 따라서 @data_out 의 data rate는 @clk 의 frequency 의 절반으로 제한됩니다. 유일한 예외는 외부 구성 요소가 @sync_clk_out의 clock edges (즉, DDR input이 있음)에 모두 민감한 경우입니다. 이는 일반적으로 그렇지 않습니다.

data outputs와 정렬된 output clock을 생성하기 위해 output DDR register를 사용할 수 있습니다. 아이디어는 clock edges모두에서 값을 변경하는 flip-flop을 사용하는 것입니다. 따라서 이러한 flip-flop은 다음과 같이 작동합니다.

always @(posedge clk or negedge clk)

if (clk)

sync_clk_out <= 0;

else

sync_clk_out <= 1;

@sync_clk_out는 @clk의 rising edge 에 반응하여 낮게 변경됩니다. falling edge로 인해 반대가 발생합니다. 결과는 동일한 frequency를 가진 output clock 입니다.

하지만 이 Verilog code는 대부분의 synthesizers와 작동하지 않을 것입니다. 왜냐하면 logic fabric 의 flip-flops는 일반적으로 두 clock edges에 모두 민감할 수 없기 때문입니다. IOB registers 만이 이 기능을 가지고 있으며, synthesizer는 이 가능성을 이해할 만큼 영리하지 못합니다.

따라서 logic primitive 의 instantiation이 필요합니다. primitive는 사용되는 FPGA 에만 해당됩니다. 이 예는 Kintex Ultrascale에서 이 작업을 수행하는 방법을 보여줍니다.

ODDRE1 ODDR_ins

(.C(clk), .Q(sync_clk_out),

.D1(1'b0), .D2(1'b1),

.SR(1'b0));

그러나 이제 clock은 output DDR register 로 생성되고 data signals는 일반 IOB registers로 생성됩니다. data 와 clock 사이의 정렬은 이전만큼 명확하지 않습니다. 따라서 모든 outputs에 대한 timing reports를 읽고 delays 간의 차이가 충분히 작은지 확인하는 것이 중요합니다.

data 에도 output DDR registers를 사용할 수 있습니다. D1 와 D2에 동일한 값이 주어지면 output은 각 clock cycle에 대해 한 번만 변경됩니다.

module top (

input clk,

output [7:0] data_out,

output sync_clk_out

);

reg [7:0] data;

ODDRE1 ODDR_ins

(.C(clk), .Q(sync_clk_out),

.D1(1'b0), .D2(1'b1),

.SR(1'b0));

ODDRE1 ODDR_data_ins [7:0]

(.C(clk), .Q(data_out),

.D1(data), .D2(data),

.SR(1'b0));

always @(posedge clk)

data <= data + 1;

endmodule

이 방법을 사용하면 data 와 clock이 정렬됩니다. output DDR registers 의 명시적 instantiation은 IOB registers가 사용되도록 보장합니다. 이 방법의 유일한 단점은 각 FPGA에 따라 다르다는 것입니다.

output DDR registers 의 동작은 예기치 않고 혼란스러울 수 있습니다. 예를 들어 @data는 @clk의 positive edge 와 동기화됩니다. 그러나 ODDRE1은 두 clock edges모두에서 활성화됩니다. 두 개의 data inputs를 샘플링하는 방법과 시기에 대해서는 FPGA 설명서를 읽어보십시오.

또한 이 예에서는 reset이 사용되지 않습니다. 이는 특히 정교한 FPGAs에서 안전하지 않을 수 있습니다. output DDR register는 IOB내부의 보다 복잡한 logic element 의 일부일 수 있습니다. 이러한 logic element는 reset없이는 올바르게 작동하지 않을 수 있습니다.

Timing constraints

이 방법에 timing constraints가 필요합니까? IOB registers덕분에 clock output 와 data outputs가 거의 완벽하게 정렬된다면 그것으로 충분하지 않을까요?

대답은 이 방법이 timing constraints없이도 완벽하게 잘 작동할 수 있다는 것입니다. 그러나 그럼에도 불구하고 timing constraints를 활용하는 것은 좋은 생각입니다. 그 이유는 IOB registers에 관한 페이지 의 동일한 주제와 동일합니다.

기타 고려 사항

그러나 IOB registers를 사용하는 것이 유일한 보장은 아닙니다. 또한 output ports사이의 물리적인 근접성에 주의하십시오. output ports가 서로 멀리 떨어져 있는 경우 이 물리적 거리는 FPGA의 clock skew 에 나쁜 영향을 미칠 수 있습니다. traces 의 길이 차이(예: PCB의 wires )도 부정적인 영향을 미칠 수 있습니다. 또한 전기적 매개변수(voltage, I/O standard, slew rate, drive current 등)는 모든 outputs에서 동일해야 합니다.

FPGA 에 IOB registers가 없으면 timing constraints가 중요합니다. source-synchronous outputs를 사용하기 위한 기본은 모든 관련 output ports사이에 낮은 skew를 보장하는 기능입니다. 일반적으로 flip-flop 와 I/O pin 사이에서 delay을 제어하는 것으로 충분합니다. 이 delay이 관련 FPGA에 가능한 최소값에 가깝다면 outputs 간의 차이는 대부분의 목적에 충분히 작을 것입니다.

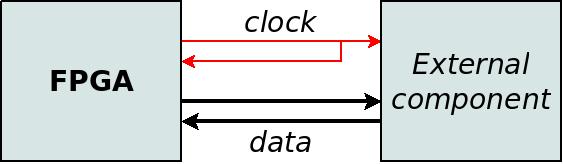

양방향 I/O

source-synchronous outputs 의 주요 특징은 관련 clock이 FPGA에서 생성된다는 것입니다. 이는 모든 data signals가 외부 구성 요소를 향할 때 분명히 적합합니다. 그러나 양방향에 data signals가 있는 경우에도 FPGA에서 생성된 clock 에 의존하는 것이 합리적일 수 있습니다.

하지만 data inputs는 PCB의 clock 와 동기화되어 있고, FPGA chip내부의 clock 와 동기화되어 있지 않다는 점에 유의하세요. 이 두 clocks는 물론 정확히 동일한 frequency를 가지고 있습니다. 하지만 output ports의 clock-to-output delay 에 따라 타이밍 차이가 있습니다. 이는 몇 나노초가 될 수 있습니다.

따라서 PCB에서 loopback을 만드는 것이 좋습니다. FPGA의 clock output을 input port에 연결합니다. 이 input port는 system synchronous clock 인 것처럼 취급할 수 있습니다. 외부 구성 요소는 clock이 FPGA가 아닌 전용 oscillator에서 온 것처럼 작동합니다. FPGA 와 외부 구성 요소가 모두 PCB의 동일한 물리적 signal 에 의존하기 때문에 이는system synchronous clock와 유사합니다.

data inputs를 source-synchronous inputs 로 취급하는 것도 가능할 수 있습니다. 특히 phase shifting 기술을 사용하면 clock loopback이 필요 없다. 이것은 실제로 DDR SDRAM memories와 인터페이스하는 일반적인 방법입니다.

중요한 결론은 PCB를 제조하기 전에 input signals 의 timing을 신중하게 계획하고 필요한 경우 clock loopback 추가를 고려하는 것입니다.