소개

이 페이지에서는 01-signal sampling을 source-synchronous input와 인터페이스하는 방법을 설명합니다. 이러한 종류의 데이터 소스와 인터페이스하는 다른 전략은 일반적으로 source-synchronous inputs 에 대한 페이지 에 설명되어 있습니다. 해당 페이지에는 source-synchronous input이 무엇인지도 설명되어 있습니다.

01-signal sampling 의 기본 아이디어는 외부 clock이 data signal로 취급된다는 것입니다. 따라서 clock은 register에 의해 샘플링됩니다. 이 register는 안정적이고 외부 clock와 독립적인 내부 clock을 사용합니다.

data signals는 추가 registers에 의해 샘플링됩니다. 이 목적을 위해 동일한 내부 clock이 사용됩니다. 이 내부 clock은 01-signal sampling을 구현하는 모든 logic 에도 사용됩니다.

이 logic은 외부 clock을 샘플링하는 register 의 변화를 감지합니다. 이 register가 '0' 에서 '1'로 변경되면 외부 clock에 rising edge가 있었다는 의미입니다. logic은 다른 registers 의 값을 FIFO에 기록하여 이 이벤트에 응답합니다. 이러한 registers 에는 외부 clock 의 rising edge가 발생했을 때 존재했던 data signals 의 값이 포함되어 있습니다.

이 logic은 FIFO의 clock이 외부 clock이 고 FIFO의 data inputs가 data signals에 직접 연결된 것과 같은 결과를 얻습니다. 차이점은 logic에서 clock을 사용한다는 것입니다. 외부 clock 또는 내부 clock. 01-signal sampling 의 장점은 모든 logic이 내부 clock에만 의존한다는 것입니다. 이 clock은 안정적이고 신뢰할 수 있습니다. 외부 clock이 오작동하더라도 logic은 계속해서 합리적인 방식으로 작동합니다.

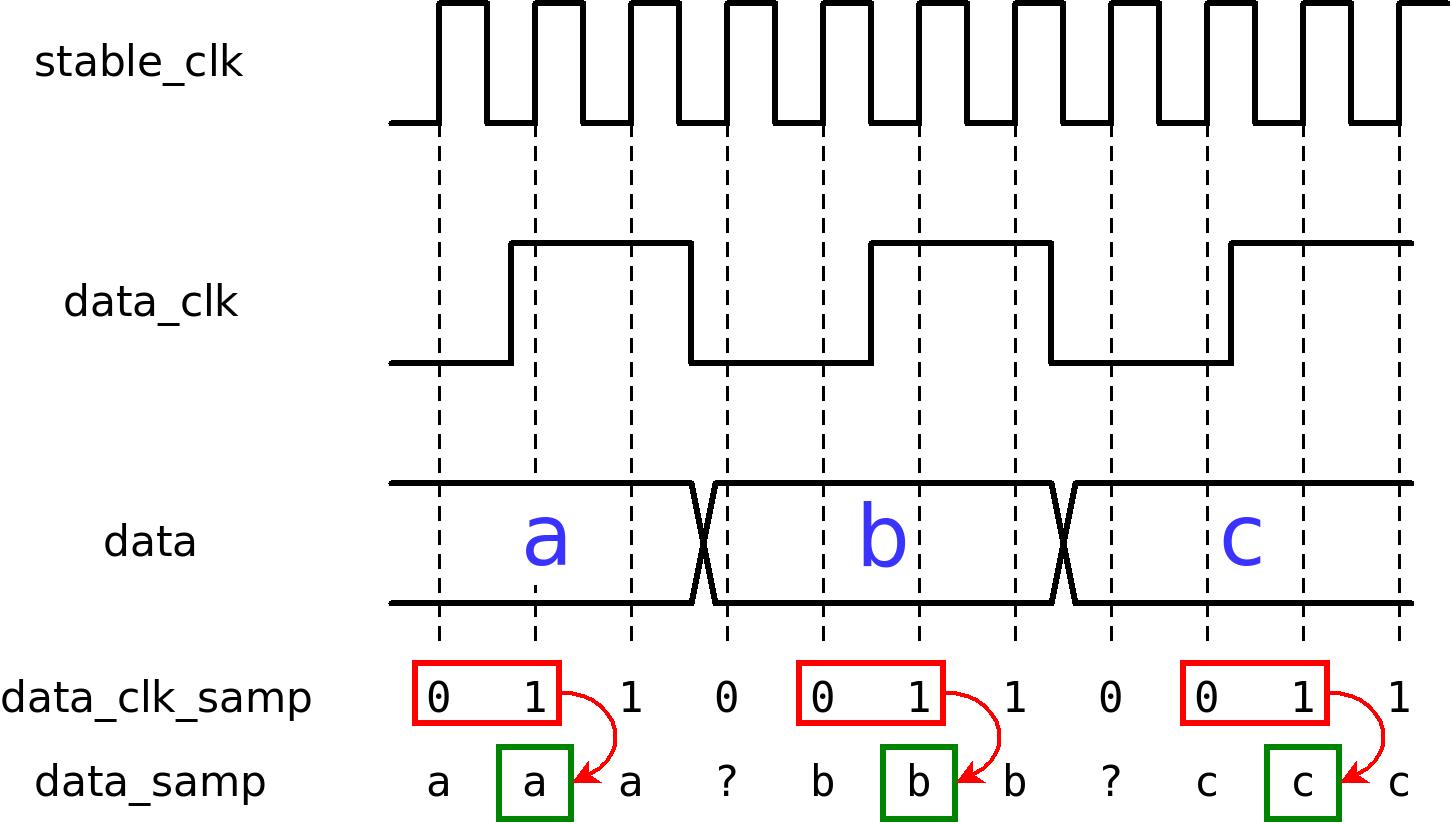

다음 이미지는 01-signal sampling을 보여줍니다.

이 이미지에서 @stable_clk은 FPGA의 내부 clock입니다. @data_clk 와 @data는 FPGA에 도착하는 signals 입니다. @data_clk_samp 와 @data_samp는 FPGA내부의 registers 입니다. 외부 signal @data_clk은 @data_clk_samp로 표현됩니다. @data와 관련하여 @data_samp 도 마찬가지입니다.

이미지는 @data_clk_samp에 "0 1" 패턴이 나타날 때 @data_samp 의 값이 FIFO에 기록되는 것을 보여줍니다. 이것이 이 방법을 "01-signal sampling"라고 부르는 이유입니다.

FIFO는 도착하는 데이터를 어떻게 처리할 것인지에 대한 예로 여기에 나와 있습니다. 이는 종종 적절한 솔루션인데, 내부 clock 의 frequency가 data rate보다 상당히 높기 때문입니다. 따라서 더 낮은 clock frequency를 기반으로 하는 logic 로 데이터를 계속 처리하는 것이 종종 편리합니다. FIFO는 다른 clock domain에서 logic 로 데이터를 넘기는 편리한 방법입니다.

그럼에도 불구하고 01-signal sampling에 사용된 것과 동일한 내부 clock을 사용하여 logic 의 나머지 부분을 구현하는 것이 가능합니다. FIFO를 사용하는 것은 하나의 가능성일 뿐입니다.

Verilog의 예

이 Verilog code는 아이디어를 보여줍니다. 외부 clock은 @data_clk입니다.

module top (

input stable_clk,

input data_clk,

input [7:0] data

);

reg [7:0] data_guard, data_samp;

reg data_clk_guard, data_clk_samp, data_clk_samp_d;

wire fifo_wr_en;

always @(posedge stable_clk)

begin

data_guard <= data;

data_clk_guard <= data_clk;

data_samp <= data_guard;

data_clk_samp <= data_clk_guard;

data_clk_samp_d <= data_clk_samp;

end

assign fifo_wr_en = data_clk_samp && !data_clk_samp_d;

data_fifo fifo_i

(

.wr_clk(stable_clk),

.din(data_samp),

.wr_en(fifo_wr_en),

[ ... other ports connected here ... ]

);

endmodule

중요한 부분은 FIFO 의 wr_en입니다. @fifo_wr_en. 이 signal은 "data_clk_samp && !data_clk_samp_d"와 같습니다. 따라서 이 signal은 @data_clk_samp에서 "0 1" 패턴을 감지한 결과 높은 수치입니다. 이로 인해 @data_samp 의 값이 FIFO에 기록됩니다.

logic에서는 @stable_clk 만 clock 로 사용됩니다. @data_clk은 일반 I/O input처럼 취급됩니다.

@data_guard 및 @data_clk_guard 의 timing requirements는 보장되지 않습니다. input ports는 @stable_clk와 비동기식입니다. 따라서 @data_guard 와 @data_clk_guard는 metastability guards입니다. logic은 이 두 registers의 가치에 직접적으로 의존하지 않습니다. 반면, @data_samp 와 @data_clk_samp는 logic에서 직접 사용되는데, 이들 registers가 metastability guard의 두 번째 단계이기 때문입니다.

하지만 이것이 전혀 작동합니까? 그 답은 timing analysis에 있습니다.

Timing analysis

01-signal sampling 의 timing analysis는 일반적인 방식과 다릅니다. 일반적으로 clock edge 와 data signals가 샘플링되는 순간 사이에는 일정한 시간 차이가 있습니다. 이는 sampling 에 사용되는 clock이 data signals와 동기화되어 있기 때문입니다. 하지만 01-signal sampling의 경우 @data 의 sampling은 @stable_clk와 이루어집니다. 따라서 sampling 의 순간은 data signals자체의 timing와 아무런 관련이 없습니다. 대신 logic은 rising clock edge에 가까운 @data_clk_samp 의 값만 선택합니다.

따라서 data clock의 rising edge 순간과 실제 sampling이 발생하는 순간 사이에는 무작위 시간 차이가 있습니다. 이 방법이 신뢰할 수 있다는 것이 어떻게 가능할까요?

logic design의 timing 기본 사항 에 대한 별도의 페이지가 있습니다. 해당 페이지에서는 tsu 및 thold의 의미를 설명합니다. 간단히 말해서, flip-flop의 input port는 clock 의 rising edge 전후에서 안정적이어야 합니다( flip-flop이 rising edge에서 활성화되었다고 가정). tsu는 rising edge이전에 input port가 안정되어야 하는 시간을 정의합니다. thold는 rising edge이후 input port가 안정되어야 하는 시간을 정의합니다. 이러한 조건 중 하나가 위반되면 rising edge 에 대한 flip-flop의 반응을 예측할 수 없습니다.

이것을 다른 방식으로 보는 것이 가능합니다: input port는 rising edge주변의 특정 기간 동안 안정적이어야 합니다. 이 기간을 Δt = tsu + thold라고 부르겠습니다. Δt 와 다른 parameters를 기반으로 이제 안정적인 작동을 보장하는 timing requirements를 찾을 것입니다.

전체 timing analysis는 @data_clk_guard가 높고 @data_clk_samp가 낮은 상황을 기반으로 합니다. 이런 일이 발생하면 "0 1" 패턴이 한 clock cycle 후에 감지됩니다. 즉, 다음 clock cycle에서는 @data_clk_samp_d가 '0', @data_clk_samp가 '1'가 됩니다. 결과적으로 @fifo_wr_en이 높아지므로 @data_samp 에는 데이터 소스가 의도한 값이 포함되어야 합니다.

따라서 분석은 다음 질문에 초점을 맞출 것입니다. @data_clk_guard가 높고 @data_clk_samp가 낮을 때 정보가 올바르게 도착하도록 보장하는 @data 에 대한 요구 사항은 무엇입니까?

분석은 두 부분으로 이루어집니다. 두 부분 모두에서 @data_clk_guard는 하이이고 @data_clk_samp는 로우라고 가정하겠습니다. 첫 번째 부분에서 질문은 다음과 같습니다. @data_clk이 이 가정을 깨지 않고 로우에서 하이로 바뀔 수 있는 가장 최근의 순간은 언제일까요? 그런 다음 @data_samp 에 올바른 값이 포함되어 있는지 확인하는 @data 와 관련된 timing requirement를 찾습니다.

분석의 두 번째 부분에서는 반대 질문을 던질 것입니다. @data_clk_guard 및 @data_clk_samp에 대한 가정을 깨지 않고 @data_clk이 로우에서 하이로 변경될 수 있는 가장 빠른 순간은 언제입니까? 그런 다음 timing requirements에 대해서도 비슷한 분석을 하겠습니다.

하지만 먼저 몇 가지 기호를 정의해 보겠습니다.

- tclk: @stable_clk의 clock period 입니다.

- tskew: 이것은 @data_clk 와 @data의 ports사이의 skew 입니다. 이것은 signals 의 소스에서 FPGA의 flip-flops까지의 모든 연결에 대한 signal delays 사이의 최대 차이입니다.

- tj: clock period에 대한 jitter 의 최대 기여. 즉, 두 clock edges 의 시간차는 항상 tclk - tj 와 tclk + tj사이의 값이 됩니다. 또는 더 정확하게는 clock period가 이러한 제한을 벗어날 가능성은 무시할 수 있습니다.

분석의 첫 번째 부분

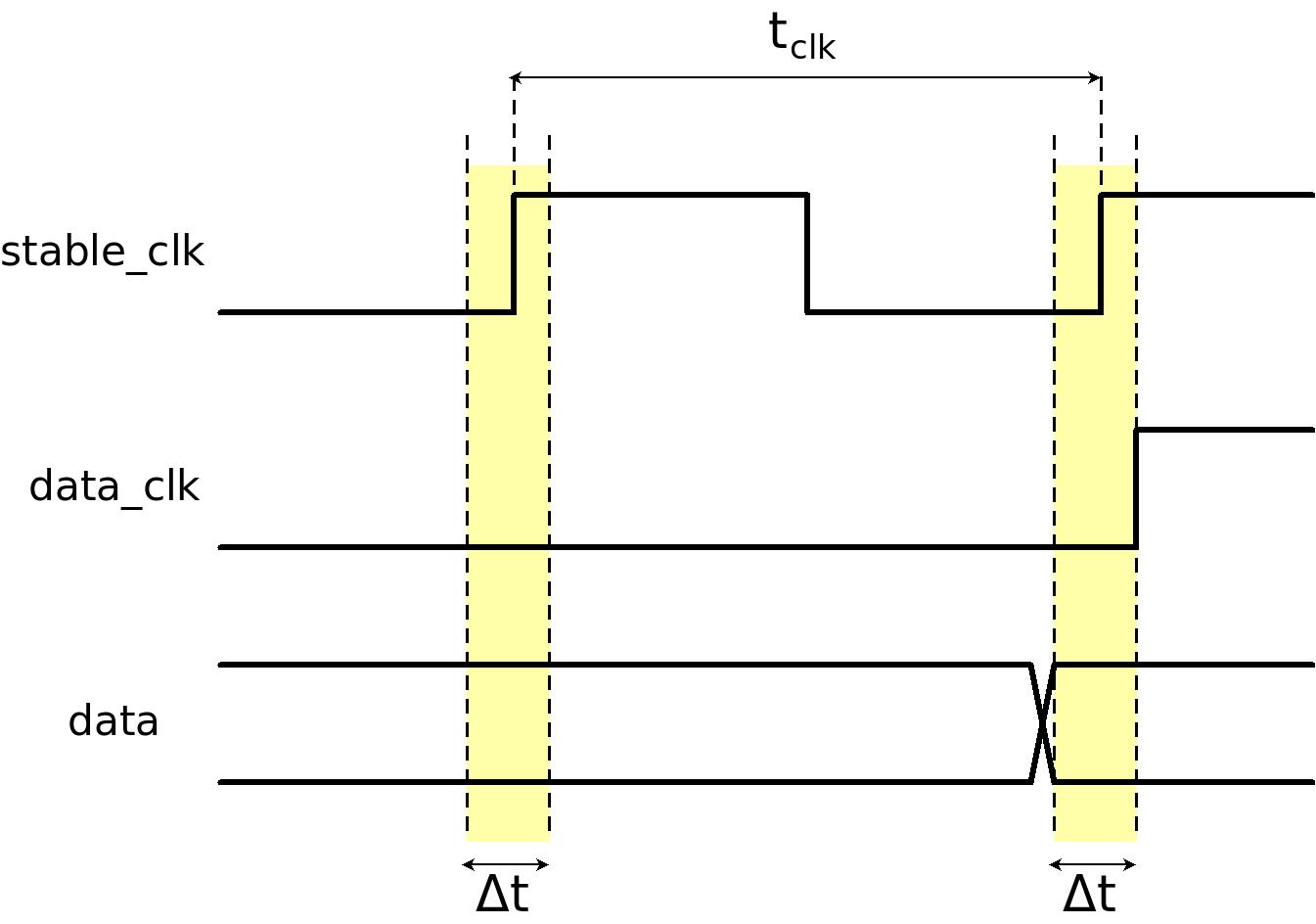

이 timing diagram은 @stable_clk두 대의 clock cycles를 보여줍니다. 아래 설명에서 @data_clk_guard는 rising edge 의 @data_clk 에서 오른쪽으로 새 값을 복사합니다. 마찬가지로 @data_guard는 @data 의 새 값을 동일한 clock edge에 복사합니다.

같은 원리로 왼쪽의 @data_clk_samp 와 @data_samp는 @stable_clk의 rising clock edge 와 연관되어 있습니다.

이 시나리오에서는 @data_clk이 노란색 영역의 끝에서 정확히 높음으로 변경됩니다. flip-flop의 timing requirements를 위반한 것이므로 결과를 예측할 수 없습니다. 그러나 @data_clk_guard는 높고 @data_clk_samp는 낮을 가능성이 있습니다.

그러나 @data_clk이 조금 나중에 값을 변경하면 flip-flop의 동작을 예측할 수 있으므로 @data_clk_guard는 확실히 낮아질 것입니다. 이 시나리오에서는 전체 노란색 기간 동안 input port가 낮습니다. 이것이 우리가 이렇게 말할 수 있는 이유입니다: @data_clk_guard가 하이이고 @data_clk_samp가 로우인 경우 @data_clk은 위의 timing diagram 에 표시된 것보다 먼저 로우에서 하이로 변경됩니다. 따라서 timing diagram은 @data_clk이 가장 늦은 순간에 변경된 시나리오를 보여줍니다.

@data_guard 에 신뢰할 수 있는 값이 포함되도록 하려면 @data가 노란색 영역 이전에 안정적이어야 합니다. 이것은 우리에게 첫 번째 timing requirement를 제공합니다. @data는 @data_clk의 rising edge이전 Δt 기간 동안 안정적이어야 합니다.

@data_clk이 낮은 수준에서 높은 수준으로 일찍 변경되는 경우에도 이 timing requirement는 여전히 @data_guard의 tsu 요구 사항을 보장합니다. 따라서 flip-flops의 tsu는 @data_clk_guard가 높고 @data_clk_samp가 낮은 모든 시나리오에서 보장됩니다.

위의 timing diagram 에는 skew와 관련된 내용이 전혀 표시되지 않습니다. skew를 고려하기 위해 timing requirement는 다음과 같습니다. @data는 @data_clk의 rising edge이전 Δt + tskew 기간 동안 안정적이어야 합니다.

이 시나리오에서는 하나의 clock edge 만 논의에 포함되었기 때문에 jitter를 고려할 필요가 없습니다.

분석의 두 번째 부분

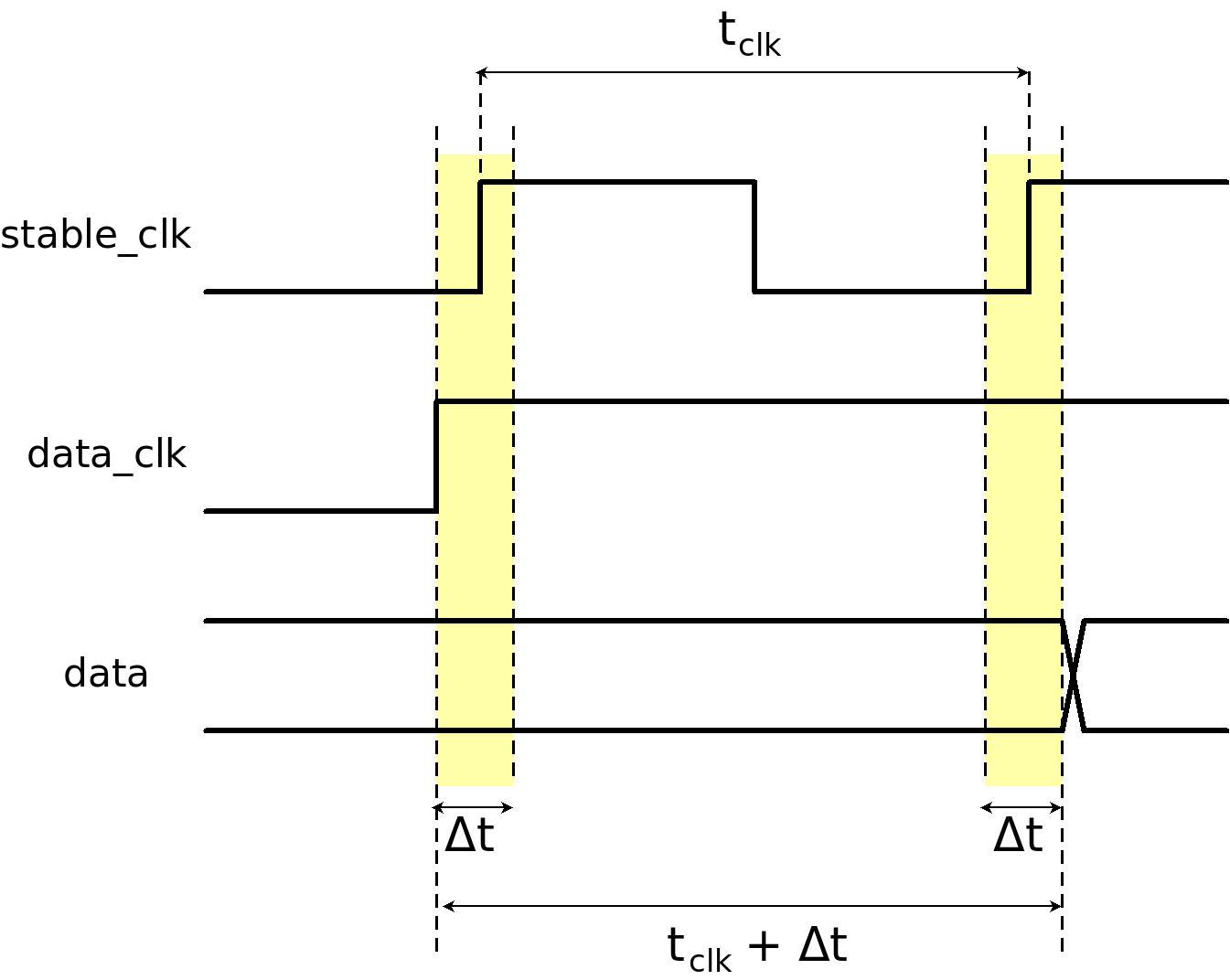

이 시나리오의 timing diagram은 다음과 같습니다.

이 시나리오에서 @data_clk은 @stable_clk의 이전 clock edge의 노란색 영역 시작 부분에서 정확히 높음으로 변경됩니다.

이 상황에서 @data_clk_guard가 높을 것이라는 데는 의심의 여지가 없습니다. 그러나 이전 clock cycle의 timing violation 때문에 @data_clk_samp 의 값은 예측할 수 없습니다. 이전과 마찬가지로 @data_clk_samp가 낮을 수 있습니다. 그러나 @data_clk이 이보다 일찍 값을 변경하면 @data_clk_samp는 확실히 높을 것입니다.

따라서 @data_clk_guard가 High이고 @data_clk_samp가 Low인 경우 @data_clk은 위의 timing diagram 에 표시된 것보다 늦게 Low에서 High로 변경됩니다. 따라서 timing diagram은 @data_clk이 가장 빠른 순간에 변경된 시나리오를 보여줍니다.

@data_guard 에 올바른 값이 포함되도록 하려면 오른쪽 노란색 영역 이후 @data가 안정적이어야 합니다.

위의 timing diagram 에 따르면 @data_clk의 rising edge 와 두 번째 노란색 영역의 끝 부분 사이의 시간 차이는 Δt + tclk입니다. 하지만 skew 와 jitter 도 고려해야 합니다. 따라서 @data는 @data_clk이후 Δt + tclk + tskew + tj 기간 동안 안정적이어야 합니다.

@data_clk이 더 일찍 낮은 수준에서 높은 수준으로 변경되는 경우에도 이 timing requirement는 여전히 @data_guard의 hold 요구 사항을 충족합니다. 따라서 flip-flops의 thold는 @data_clk_guard가 높고 @data_clk_samp가 낮은 모든 시나리오에서 보장됩니다.

timing requirements

위에서 timing analysis를 결론적으로 말하자면 01-signal sampling의 안정적인 작동을 보장하는 두 가지 timing requirements는 다음과 같습니다.

- @data는 @data_clk의 rising edge이전에 최소 Δt + tskew 기간 동안 안정적이어야 합니다.

- @data는 @data_clk의 rising edge이후 최소 Δt + tclk + tskew + tj 기간 동안 안정적이어야 합니다.

이러한 요구 사항은 복잡해 보일 수 있지만 이를 충족하는지 확인하는 것은 쉬운 경우가 많습니다. 예를 들어 @data가 @data_clk의 falling edge와 함께 변경되는 경우 일반적으로 이러한 요구 사항을 쉽게 충족할 수 있습니다. @stable_clk이 @data_clk보다 3배 빠르다면 그것만으로도 충분합니다.

대부분의 경우 Δt, tskew 또는 tj의 정확한 값을 알 필요가 없습니다. 위의 두 가지 요구 사항에 따라 Δt 와 Δt + tskew + tj가 얼마나 크게 허용되는지 계산하는 것으로 충분한 경우가 많습니다. @stable_clk의 frequency가 충분히 높으면 이 두 표현식의 값은 FPGA에 대해 현실적으로 가능한 것보다 더 큰 경우가 많습니다.

FPGA의 input ports (tskew) 간의 timing 차이를 최소화하려면 IOB registers를 사용해야 합니다. 또한, IOB registers 의 사용을 보장할 목적으로 이러한 input ports 와 관련하여 timing constraints를 작성해야 합니다.

01-signal sampling의 변형

지금까지의 논의에서는 @data가 data_clk의 falling edge와 함께 변화한다고 가정했습니다. @data가 @data_clk의 rising edge와 함께 변경되면 @data_clk_guard가 로우이고 @data_clk_samp가 하이일 때 대신 활성화되도록 logic을 조정해야 합니다. 즉, logic은 "1 0" 패턴을 찾아 @data_clk 의 falling edge를 감지해야 합니다.

@data의 값을 얻을 때 다른 기준을 선택할 수도 있습니다. 예를 들어, @fifo_wr_en을 몇 clock cycles만큼 지연시키는 것이 더 나을 수 있습니다. 때로는 @fifo_wr_en이 위에서 제안한 것보다 일찍 활성화되는 것이 더 좋습니다. 이는 @data_clk 와 @data간의 타이밍 관계에 따라 달라집니다. 신호 소스의 datasheet을 참조하고 위에 표시된 대로 timing을 분석합니다.

@data_clk의 frequency가 비교적 높으면 DDR registers를 사용하여 @data_clk 와 @data를 샘플링할 수 있습니다. 이 솔루션을 구현하는 logic은 조금 더 복잡하지만 동일한 원칙이 적용됩니다.

@data_guard는 정말 metastability guard인가요?

이 질문에 대한 짧은 대답은 '예'입니다. @data는 @stable_clk와 비동기식이므로 @data_guard의 timing requirements는 보장되지 않습니다.

하지만 @data_guard의 콘텐츠가 실제로 사용되는 clock cycles 로 논의 범위를 좁혀 보겠습니다. 위의 두 timing requirements는 @data_guard를 구현하는 flip-flops가 안정적으로 작동하도록 보장합니다. 이 flip-flops 의 tsu 와 thold 모두 보장됩니다.

따라서 @data_guard는 실제로 metastability guard로 사용되지 않습니다. 이 register가 사용되는 방식에서는 delay register로만 기능합니다. 하지만 여분의 register가 물리적인 signal (@data)가 잘못 작동할 경우 발생할 수 있는 timing violations 로부터 보호한다는 점은 해롭지 않습니다. 이는 특히 signal이 커넥터를 통해 FPGA 에 연결된 경우에 해당합니다.

실제 사례

다른 페이지 에 OV7670 camera sensor 와 연결되는 logic 의 예가 있습니다. 이 logic은 01-signal sampling덕분에 이 카메라 센서에서 pixel data를 얻습니다. 카메라 센서의 inputs는 다음과 같습니다.

input pclk_in;

input [7:0] D_in;

input hsync_in, vsync_in;

01-signal sampling을 수행하는 logic은 다음과 같습니다.

(* IOB = "TRUE" *) reg [7:0] D_guard;

(* IOB = "TRUE" *) reg pclk_guard, hsync_guard, vsync_guard;

reg [7:0] D;

reg pclk, hsync, vsync;

wire sample_valid;

reg previous_pclk;

always @(posedge stable_clk)

begin

// Metastability guards on asynchronous inputs

D_guard <= D_in;

pclk_guard <= pclk_in;

hsync_guard <= hsync_in;

vsync_guard <= vsync_in;

D <= D_guard;

pclk <= pclk_guard;

hsync <= hsync_guard;

vsync <= vsync_guard;

previous_pclk <= pclk;

end

assign sample_valid = pclk && !previous_pclk;

명확성을 위해, 여기에 제시된 Verilog code 와 OV7670에 대한 페이지 의 Verilog code 사이에 약간의 차이가 있습니다. 이러한 차이점은 logic 의 작동 방식에 영향을 미치지 않습니다.

이 Verilog code를 이 페이지 맨 위에 제시한 code 와 비교해 보겠습니다. signals 의 이름은 다르지만 의미는 같습니다. @data대신 @D_in, @hsync_in , @vsync_in이 있습니다. @data_clk대신 @pclk_in이 있습니다. @fifo_wr_en대신 @sample_valid가 있습니다. 이름의 변화는 혼란스러울 수 있지만 위의 Verilog code 와 아무런 변화가 없습니다.

registers선언 앞의 "(* IOB = "TRUE" *)" 부분을 참고하세요. Vivado사용시 IOBs에 registers를 끼워달라고 요청할 수 있는 방법입니다.

이 예에서는 FIFO가 표시되지 않습니다. 이는 FIFO에 모든 데이터를 쓰고 싶지 않기 때문입니다. @sample_valid가 높으면 @D, @hsync 및 @vsync가 카메라 센서의 올바른 값을 포함한다는 의미입니다. 하지만 이것이 @D를 FIFO에 쓰고 싶다는 의미는 아닙니다. @hsync 및 @vsync에 따라 다릅니다. 따라서 OV7670 의 예에는 FIFO에 픽셀만 기록되도록 하는 추가 logic이 있습니다.

하지만 흥미로운 부분을 살펴보겠습니다. timing analysis.

이 예에서 @stable_clk 의 frequency는 100 MHz입니다. @pclk_in 의 frequency는 25 MHz입니다. OV7670의 datasheet에 따르면, 신호 @D_in, @hsync_in 및 @vsync_in은 @pclk_in이 하이에서 로우로 변경된 후(falling edge) 5 ns 동안 안정되는 것이 보장됩니다.

@pclk_in의 clock cycle은 40 ns입니다. 따라서 falling edge 에서 rising edge 까지의 거리는 20 ns입니다. 이제 timing requirements와 비교해 보겠습니다.

첫 번째 timing requirement는 @D_in, @hsync_in 및 @vsync_in이 @pclk_in의 rising edge이전 Δt 기간 동안 안정적이어야 한다는 것이었습니다. 실제로 이러한 신호는 falling edge이후 5ns부터 안정적입니다. 따라서 이러한 신호는 다음 rising edge이전에 최소한 15 ns 에서 안정적입니다. Δt = tsu + thold를 기억해 보세요. 그래서 timing requirement는 실제로 tsu + thold가 15 ns보다 작다는 것입니다. 이는 모든 FPGA에 해당됩니다.

두 번째 요구 사항은 이러한 신호가 @pclk_in의 rising edge이후 최소한 Δt + tclk + tskew + tj 시간 동안 안정적이어야 한다는 것입니다. 그러나 이러한 신호는 falling edge의 결과로만 변경됩니다. 따라서 요구 사항은 Δt + tclk + tskew + tj가 20 ns보다 작다는 것입니다. tclk은 10 ns 와 같습니다. 왜냐하면 @stable_clk의 frequency가 100 MHz가 기 때문입니다. 따라서 실제 요구 사항은 Δt + tskew + tj가 10 ns보다 작다는 것입니다. 다시 한 번 말하지만, 이는 모든 FPGA에서 명백합니다.

이 예는 FPGA의 정확한 timing parameters에 대한 지식 없이도 timing requirements를 쉽게 보장할 수 있는 방법을 보여줍니다.

결론

FPGA가 지원할 수 있는 clock frequency 에 비해 data rate가 낮은 경우01-signal sampling은 탁월한 솔루션입니다. data clock은 안정적일 필요가 없습니다. 또한 data clock 의 정확한 frequency는 미리 알 필요가 없습니다. 두 개의 timing requirements를 보장하는 것으로 충분합니다.

이 방법에는 다음과 같은 추가 장점이 있습니다. 이 clock이 잠깐 비활성화되면 유일한 결과는 해당 특정 기간 동안 data가 수집되지 않는다는 것입니다. 이 clock 의 모든 오작동으로 인한 피해는 데이터 흐름의 중단으로 제한됩니다. 이는 시스템의 눈에 띄는 오작동으로 이어지지만 이 오작동은 clock 의 문제처럼 보입니다( FPGA가 유령에게 괴롭힘을 당하는 것처럼 보이지는 않습니다).

따라서 data signals 의 sampling 에는 내재된 임의성이 있지만 01-signal sampling은 source synchronous input을 위한 안정적이고 강력한 솔루션입니다. 유일한 단점은 data rate의 한계입니다.