このページは、 Multi-Gigabit Transceiver (MGT) を紹介する一連のページの6 番目であり、 PMAに関する 2 番目のページです。

序章

前のページでは、 PMA を使用した物理チャネルを介した bits の送信について説明しました。ただし、このデータ ストリームは常にオンになっているわけではありません。 電力を節約するために、 MGT の大部分をオフにすることができます。これは、 MGT がラップトップ コンピューター内に SATA、 PCIe、または SuperSpeed USB を実装している場合に特に重要です。これらの protocols が適用されている場合、送信するデータがないときに物理リンクをアクティブにしておくと、エネルギーの無駄になります。

したがって、 MGT は低電力状態に移行する機能を備えている必要があります。さらに重要なのは、 MGT がこの低電力状態から復帰するタイミングを相手側に通知する機能を備えている必要があることです。 PMA は、この目的 (およびその他の目的) のために OOB signals を生成および検出する役割を担っています。

Out-of-band (OOB) 信号は、データ ストリームの送信に使用される同じ差動ワイヤ上の単純な電気活動パターンで構成されます。これらの OOB 信号は、通常のデータ ストリームがオフになっている場合にのみ送信できます。これらの信号で最も重要なことは、非常に単純な logicの助けを借りて受信機が検出できることです。これにより、 OOB 信号を受信する MGT は、この MGT が低電力状態にある場合でもそれを検出できます。

MGTs がサポートするもう 1 つの機能は、送信機が別の MGT に物理的に接続されているかどうかを検出する機能です (他の MGT に何もさせる必要はありません)。この機能はReceiver Detectionと呼ばれます。

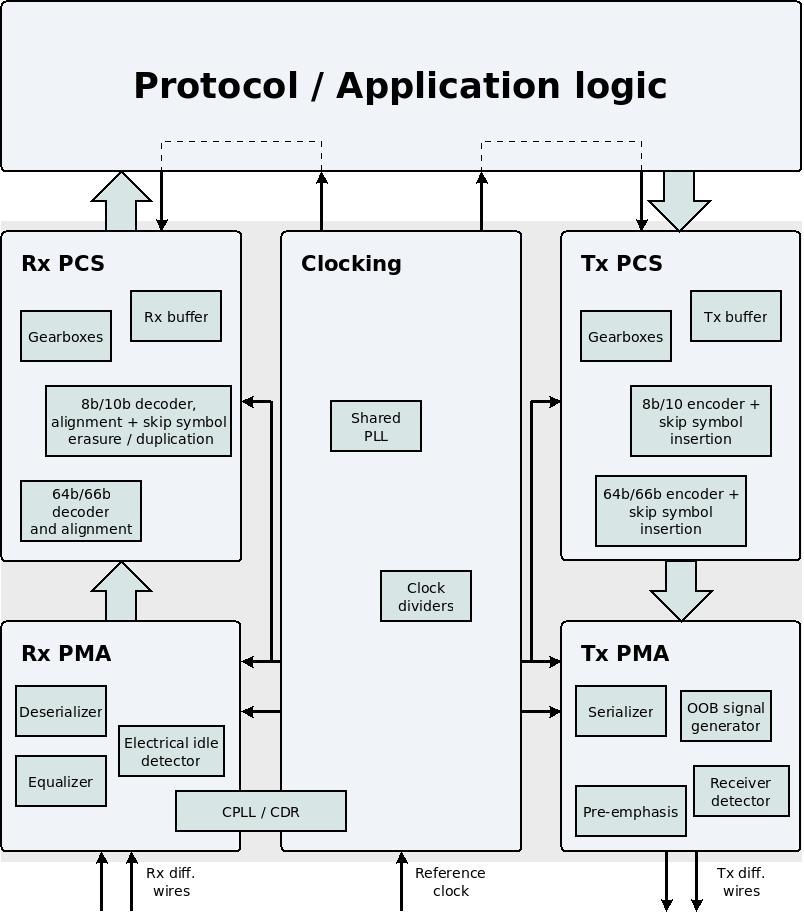

このページでは、次の 2 つの機能を紹介します。 OOB signals と receiver detection。便宜上、前の 2 ページのブロック図を再度示します。

OOB signalsの送信

Out-Of-Band (OOB) 信号は通常、一定の frequencyを持つ単純な方形波信号です。この signal は、通常のデータ ストリームの代わりにのみ送信でき、同時に送信することはできません。

protocol ごとに、 OOB signalの形状に関する要件が異なります。 FPGA MGT には通常 input ports があり、 application logic は最も一般的に使用される protocols (特にPCIe と SATA ) に従って OOB signals を要求できます。

OOB signals の命名法と要件は、 protocol ごとに異なります。例:

- PCIe protocol は、 OOB signal を「Beacon」と呼んでいます。要件は、 30 kHz と 500 MHzの間に frequency を持つ方形波信号で満たすことができます。ただし、 protocol では、 signal が周期的であることさえ要求されません。 Beacon は、低電力状態から起動するために使用されます。

- SATA protocol は 3 種類の OOB signalsを定義します。 COMRESET、 COMINIT、および COMWAKE。 protocol は、これらの signalの構成を正確に定義します。 COMRESET は、デバイスをリセットするために host 側で使用されます。 COMINIT はデバイスによってのみ送信され、リンクを初期化するために使用されます。 COMRESET と COMINIT は signalとまったく同じですが、その意味はどちらの側が送信するかによって異なります。 COMWAKE は、どちらの側でもリンクを低電力状態から起動するために使用されます。

- USB SuperSpeed protocol は、 OOB signal を「Low Frequency Periodic Signaling」(LFPS) と呼びます。これは、 10 MHz と 50 MHzの間に frequency がある方形波です。この signal は、低電力状態を終了するために使用されますが、他のさまざまな目的にも使用されます。特に、データ ストリームの初期セットアップは、厳密に定義された LPFS signalsの交換で構成されます。 protocol は、 LFPS signalsのいくつかのパターンを定義し、各パターンは異なる意味を持ちます。たとえば、 host が 100 ms中に LFPS signal を連続して送信する場合、これはデバイスをリセットするための要件です。

MGT には、特定の protocolに適した OOB signal を生成する機能がない場合があります。これは、データ送信用のトランスミッターをオンにし、必要な信号パターンに対応するデータ ストリームを MGT に供給することで解決できます。特に、 MGTのエンコード機能がオフになっている場合、 MGT は単純な SERDESのように動作します。その後、送信データを使用して、必要な信号パターンを任意に形成できます。たとえば、連続したシーケンス「0」と「1」を送信することで、方形波を生成できます。このソリューションの主な欠点は、 MGTのエンコード機能が使用されないことです。そのため、エンコード機能は代わりに application logic に実装する必要があります。

Electrical idle

MGTの送信機がオフになっているか低電力モードになっている場合、その output は通常 electrical idle 状態になります。つまり、送信機は両方の差動出力線 (D+ と D-) を groundに接続します。したがって、これらの線間の電圧はゼロですが、各線の groundに対する電圧もゼロになります。

MGT がスリープ状態の場合、 electrical idle の状態は OOB signalの送信の反対になります。つまり、送信機の 3 つの可能な状態をまとめると次のようになります。

- データの送信。 MGT は、この状態のときのみ電源がオンになっているとみなされます。

- OOBのトランスミッション

- Electrical idle

すでに上で述べたように、 OOB は、低電力状態から相手側を起動するため、またはリンクの起動の一部として、たまにしか使用されません。そのため、ほとんどの場合、 MGT はデータを送信しているか、 electrical idle 状態でスリープしています。

OOB signalsの検出

MGT がオフになっているか低電力状態にある場合、その受信機は、反対側から OOB が送信されているかどうかを検出する必要がある場合があります。これは、特に、通常の動作を再開する要求に応答するために必要です。

ほとんどの protocols は、 OOB signalの waveform を正確に指定せず、可能性の範囲を定義します。したがって、受信側は、到着した signal を予想される waveformと比較することはできません。代わりに、差動ワイヤでアクティビティが発生したときに OOB signal が検出されます。つまり、データ ストリームがオフになっているが、差動ワイヤの電圧が electrical idleと見なすには変化が大きすぎる場合は、反対側から OOB signal が送信されているという説明になります。

このため、 FPGA MGT には OOBを検出するための output port がありません。代わりに、受信機が electrical idleを検出したときにハイになる output port があります。この port の名前は通常、「rx_elecidle」のようになります。

残念ながら、 MGTの electrical idle 検出メカニズムは信頼性が低い場合があります。特に、相手側がデータ ストリームを送信する場合、受信側の electrical idle 検出器の動作は、 MGT ごとに異なります。 この状況では、 MGT が electrical idle を検出する可能性があります。同様に、 MGT が electrical idle が存在しないことを確実に検出する可能性もあります。ランダム検出が発生する可能性もあります。 FPGA はそれぞれ動作が異なります。

理論上は、これは問題ではありません。データ ストリームがアクティブなときに electrical idle をチェックする必要があるでしょうか。しかし、現実には、 MGT は、相手側がデータを予期していない場合でもデータを送信する可能性があります。したがって、 application logic は、相手側がオフになっていると予期しているのに、代わりに通常のデータ ストリームが到着した場合に正しく反応するように設計する必要があります。

electrical idle の検出に関するもう 1 つの問題は、ノイズに対する感度です。 完璧な electrical idle は、両方の差動ワイヤの電圧がゼロのときです。ノイズの結果、受信機は electrical idleを除外するのに十分な電圧を測定する可能性があります。その場合、 application logic はこれを OOB signalと解釈するリスクがあります。

結論として、 OOB signals を確実に検出するための簡単な解決策はありません。 application logic は、 electrical idle 検出器の欠陥を補うように設計する必要があります。

Receiver detection

PCIe protocol および SuperSpeed USB には、リンクの反対側に何かが接続されているかどうかを検出する機能が必要です。この検出は、反対側との通信を開始しようとせずに実行する必要があります。この機能はreceiver detectionと呼ばれます。

これは SuperSpeed USBに必要です。コンピュータはデバイスが物理的に切断されたことを知る必要があるためです。リンクが低電力状態のときにこのような切断が発生した場合、コンピュータは何かが起こったことを知る方法がありません。 いずれにしても、ワイヤ上でアクティビティが発生することは想定されていません。したがって、 protocol では、 host が 100 msごとに受信機検出を実行する必要があります。これにより、コンピューターはエネルギーを無駄にすることなく、デバイスがまだ接続されていることを確認できます。

PCIe protocol では、この slotに接続されている可能性のあるデバイスとのリンクを確立する前に、各 PCIe slot で receiver detection を実行する必要があります。リンクを確立するには、データ送信のために MGT (正確には training sequence) の電源をオンにする必要があるため、不要な試行を避けることはエネルギーを節約するために重要です。

MGTの送信機は、両方の output wires (D+ と D-) に短い電圧パルスを生成することによって receiver detection を実行します。これは common mode 電圧パルスなので、 ground を基準とした同じ電圧が両方のワイヤに適用されます。反対側に受信機がある場合、測定可能な current が受信機の終端抵抗器を流れます。この current は送信機の outputの電圧に影響します。反対側に受信機がない場合、 current は無視できます。したがって、送信機はパルスの開始直後に output の電圧を測定し、それに応じて反対側に受信機が存在するかどうかを判断します。

パルス (単純な DC 電圧ではなく) が必要な理由は、送信機と受信機の間にコンデンサがあるためです。パルスの直後、パルス電圧が送信機と受信機の終端抵抗に降下すると、電流が流れます。コンデンサが充電されると、 current は他の RC circuitと同様に低くなります。電圧が一定であれば、 current は最終的にゼロになります。

重要なのは、 receiver detection は、 D+ と D-の両方で、受信機の終端抵抗が ground に接続されている場合にのみ機能することです。たとえば、 PCIe protocol では、これらの終端抵抗が 50Ωである必要があります。 groundに接続せずに、 D+ と D-の間に 100Ω 抵抗を接続することで、同じ差動インピーダンスを実現できます。このように終端すると、 receiver detectionを除くすべての機能が正常に動作します。違いは、他のすべての機能が D+ と D-間の差動電圧に依存しているのに対し、 receiver detection は両方のワイヤに同じ電圧を印加することで実装されていることです。終端抵抗が真ん中の ground に接続されていない場合、 current は流れず、受信機は検出されません。

これで、 MGTsに関するこのシリーズの 6 ページ目は終了です。次のページでは、 MGTの clockingについて少し説明して、このシリーズを終了します。