このページは、 Multi-Gigabit Transceiver (MGT) を紹介する一連のページの 5 番目です。多くのトピック (および FPGAsのいくつかの protocols のリスト) を確認した後、 PMA がデータを電気信号に変換する方法と、その逆の方法について説明します。

序章

PMA は、 MGT 内の物理チャネルに関連する部分で構成されています。最も注目すべきは、 serializer と deserializer が PMAの一部であることです。つまり、物理チャネルの bits とパラレル ワード間の変換は、 PMA内で行われます。

PMA は、 bits を電圧に変換する部分でもあります。同様に、反対側の MGT からの電圧を受信し、これを bitsに変換する部分でもあります。

PMA のもう 1 つの重要な役割は、この信号が 2 つの MGTs間を移動するときに発生する電圧信号の歪みを補正することです。

- 送信機は、送信用に作成したアナログ信号を意図的に歪ませる場合があります。送信機の歪みは、物理チャネルが信号に対して行う動作と逆の動作を行おうとするものです。これは、 pre-emphasisと呼ばれることがよくあります。

- 受信機の equalizer は、物理チャネルによって発生する歪みを軽減するために、到着したアナログ信号を操作する場合があります。

このページでは、これらの機能について説明します。 PMA は、データ ストリームがオフになっている場合にのみ関連する他のタスクも担当します。これらのトピックについては、次のページで説明します。

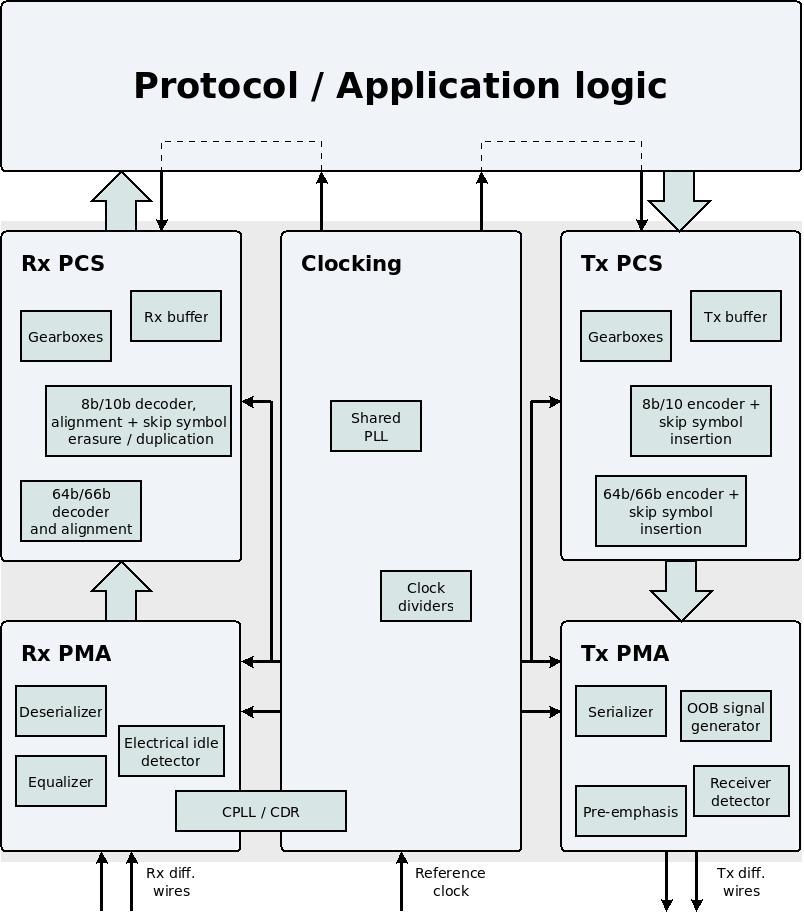

これは典型的な MGTのブロック図であり、 PMAの位置をより大きなコンテキストで示すためにここで再度示されています (この図は前のページと同じです)。

また、前のページと同様に、 MGT 内のデータ送信に使用される部分に関連して、 Tx PMA および Tx PCS という表現を使用します。同様に、データ受信には Rx PMA および Rx PCS を使用します。

使用シナリオの大部分では、物理チャネル、信号がどのように歪むか、この歪みがどのように修正されるかについて理解する必要がないことに留意することが重要です。通常、知っておく必要があるのは、 equalizer を使用するのが良いアイデアであるということだけです。

とはいえ、 PMA は大部分がアナログ コンポーネントであることを認識することが重要です。 MGT には通常、 FPGA chipに個別の電源 pins があります。これらの pins の一部は PMA に電力を供給します。これらの pins の電圧は、通常よりもクリーンであることが求められることがよくあります。これらの要件を満たさないと、 MGTのパフォーマンスが大幅に低下する可能性があります。

以下の説明では、 5 Gb/s 通信リンクについて見ていきます。これは、 SuperSpeed USB Gen 1 や PCIe 2.0と同様に、 protocols で使用されるデータ レートです。また、 PMA と PCS 間で使用されるパラレル ワードは 32 ビット幅であると仮定します。このページの後半で説明する詳細の一部を省略し、物理チャネルの簡略化した説明から始めます。

データの送信

Tx PMA は、パラレル ワードを LSBから送信して電気信号に変換します。したがって、 bit 0 が「1」の場合、 Tx PMA は output pins を調整して、 D+ と D- 間の電圧が 500 mV (例) になるようにします。この bit が「0」の場合、この電圧は -500 mV (負) になります。

Tx PMA は 0.2 nsを待機し、次にパラレル ワードの bit 1 に対して同じことを行います。つまり、 D+ と D- 間の電圧は、 bit 1に応じて 500 mV または -500 mVのいずれかになります。このように、パラレル ワードの bits のそれぞれは、 0.2 nsの期間、 output pins で表されます。 6.4 nsの後、パラレル ワード全体がワイヤ上で送信されます。 Tx PMA は、 Tx PCSから新しいパラレル ワードを受信し、同じ方法でその値の送信を開始します。

Tx PCS から Tx PMA へのパラレル ワードの転送は、 clock (多くの場合、 XCLKと呼ばれます) と同期されます。この例では、この clock の clock cycle は 6.4 nsなので、その frequency は 156.25 MHzです。当然ですが、 156.25 × 32 = 5000です。

ここで説明したのは、 SERDESの送信側です。この SERDESの output の各 bit に割り当てられる時間は 0.2 nsであり、データ レートは 5 Gb/sになります。

この例では、2 つの差動 output pins 間の電圧は 500 mVでした。これは、 PCIe と SuperSpeed USBの許容範囲内です。プロトコル仕様と MGTの datasheets では、通常、この電圧は differential peak-to-peak voltageで指定されることに注意してください。これは、最低差動電圧と最高差動電圧の差、つまりこの例では -500 mV と 500 mV の差です。したがって、この例では、 differential peak-to-peak voltage は 1000 mVです。これは、仕様に通常表示される数値であり、 datasheetsです。

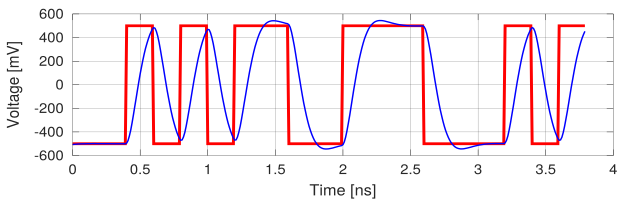

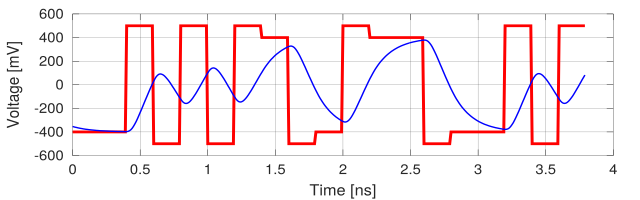

しかし、信号は受信機に到達するまでに変化しています。下の画像は、アナログ信号の waveformの例を示しています。

送信機の output ( D+ と D-間の電圧) は赤で示されています。青色の waveform は、この信号が受信機に到達する方法の例です。この例は、帯域幅が 2.5 GHzの単純な low-pass filter のシミュレーションを示しています。

このページでは、データ レートが 5 Gb/s 、差動電圧が 500 mVの例を使用します。もちろん、他の数値も可能です。 FPGA MGT を使用すると、データ転送速度と output 電圧を制御できます。

eye diagram

上の画像の waveforms は、受信機に到着する信号が送信機によって生成された信号と異なることを示しています。 eye diagram は、受信機に到着する信号のグラフ表現です。このグラフは、同じ軸に複数の waveforms を描くことで作成されます。このような各 waveform は、送信された bitsのランダムな組み合わせの結果です。したがって、グラフ上の重なり合った waveforms は、到着する信号のすべての可能な形状を表しています。

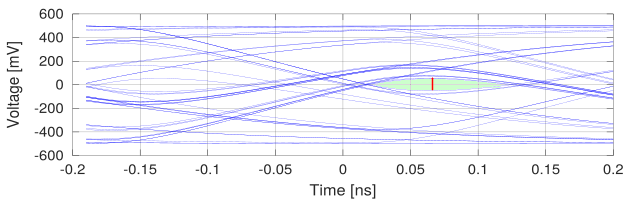

これは、上の画像と同じシナリオの eye diagram です。

この画像を見ると、なぜこれが「eye diagram」と呼ばれるのかが分かります。中央の緑色の部分は目の形をしています。

赤い線は、送信された bit が「0」か「1」かを判断するために電圧を測定する最適なタイミングを示しています。この時点で電圧差が最大になるため、ノイズに対する耐性が最も高くなります。選択された瞬間はゼロより少し後であることに注意してください。これを前の画像と比較してください。 この時点で検出される bit は、 0.2 ns中にすでに送信されており、検出はさらに少し遅れて発生します。

eye diagram は、受信機に到達する信号の品質を評価するためによく使用されます。このグラフは、信号を伝送する物理メディアのシミュレーションで作成されることがよくあります。オシロスコープやより特殊な測定機器を使用して実際の信号を測定して、 eye diagram を取得することもできます。

データの受信

Rx PMA は電気信号をパラレルワードに変換します。 Rx PMA は、 0.2 nsの時間周期ごとに 2 つの input pins (D+ と D-) ) 間の電圧を測定します。この電圧が正の場合、並列ワードの bit 0 に '1' が割り当てられます。それ以外の場合、この bit は '0' になります。 Rx PMA は、 bit 1 から bit 31まで、並列ワードの他の bits に値を割り当て続けます。並列ワードが完了すると、 Rx PMA はそれを Rx PCSに渡します。したがって、 Rx PMA は Tx PMAのミラー イメージです。

しかし、 Rx PMA はどのようにして input pinsの電圧を測定するタイミングを正確に知るのでしょうか? これは 0.2 nsの期間ごとに 1 回発生するはずですが、この期間内の正確なタイミングはいつでしょうか? Rx PMA はどのようにして上記の eye diagram の赤い線で示された最適なタイミングを認識するのでしょうか?

さらに事態を複雑にしているのは、 Rx PMA は Tx PMA が依存する reference clock にアクセスできないことが多いことです。そのため、 0.2 ns がどのくらいの時間続くかという受信機の認識は、同じ質問に対する送信機の見解とまったく同じではありません。また、この reference clockの frequency は、 jitterにより常にランダムに変化します。そして、 SSC (Spread Spectrum Clock) を必要とする protocols の場合、この clockの frequency は、事前に定義されたパターンに従って意図的に連続的に変化します。

この問題の解決策は、 Clock Data Recovery (CDR) です。これは、 input pinsの電圧をサンプリングするための最適なタイミングを見つける、 Rx PMA 内部のメカニズムです。 CDR は、到着するデータ ストリームに適応する sampling clock を生成します。この clock は、 Tx PCSとのインターフェイスに使用される clock を生成するために、 32 (この例では) で除算されます。

CDR は、到着するアナログ信号における「0」と「1」間の遷移に敏感です。より正確には、 CDR は 2 つの differential pins 間の電圧が正と負の間で変化したときにそれを検出します。これにより、 CDR は、生成する sampling clock の frequency を、送信機が使用する clock に適合させることができます。

適切に動作するために、 CDR には独自の reference clock が必要です。この reference clockの frequency は、送信機の clock frequencyとほぼ同じである必要があります。ただし、この reference clock は、データ ストリームとの初期同期にのみ使用されます。この初期同期の後、 CDR は PLLの助けを借りて送信機の frequency に従います。この適応メカニズムは、送信機の clockのレプリカを作成するために、 sampling clockの frequency をわずかに継続的に変更します。それに加えて、 CDR は、 0.2 nsの各期間内で、 sampling の瞬間を最適なポイントに移動しようとします。言い換えると、 CDR は、信号の sampling が上記の eye diagram の赤い線で発生するように努めます。

CDR は、信頼性の高い通信リンクを得る上で重要な役割を果たします。たとえば、送信機が jitterレベルの高い低品質の reference clock を使用すると、各 bitの期間の長さにランダム性が加わります。受信機の CDR がこのランダム性に十分迅速に適応できない場合、 sampling は最適でない位置で発生します。その結果、エラーの可能性が高まります。 CDR が完全に同期を失い、通信リンクが一時的に失われる可能性もあります。このような状況は、低品質の clockではなく、データ ワイヤの signal integrity の問題であると誤解されることがよくあります。

FPGA MGTでは、 CDRの動作は、設定可能ないくつかの parameters に依存します。残念ながら、これらの parameters の意味は通常複雑で、文書化されていません。 FPGA tools は、 MGTの設定に基づいて、これらの parameters の値を自動的に選択します。これは、特にデータ レートに依存します。特定のよく知られている protocol が選択されると、 CDRの parameters がそれに応じて選択されます。特に、2 つの MGTs間の接続に低品質のケーブルやコネクタがある場合は、より安定したリンクを得るために、さまざまな設定をテストすると効果的です。

polarityの反転

Rx PMA と Tx PMA はどちらも、物理チャネルの polarity を反転する可能性をサポートしています。つまり、「1」の代わりに「0」を送信するか、その逆を行います。または、「0」が通常受信されるときに「1」を受信するか、その逆を行います。

つまり、 D+ と D- の配線が入れ替わった場合、 MGT はこれを補うことができます。これは些細なことですが、非常に重要な機能であり、多くの場合、 PCB の設計を簡素化します。

信号の歪み

理想的な世界では、送信側の MGT からの電圧信号は、受信側の MGT に何の変化もなく到着します。実際には、信号は目的地に到着するまでにいくつかの変化を経ます。最も顕著な問題は、信号パスのフィルタリング特性です。 Tx PMA が「1」の後に「0」を送信するたびに、正電圧から負電圧への急激な遷移が発生します。もちろん、「0」から「1」への遷移では逆のことが起こります。この急激な電圧変化は、信号を運ぶ物理媒体によって歪められます。ケーブルと PCB traces は low-pass filterのように動作します。

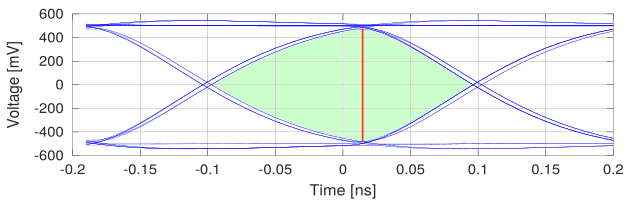

この画像は上記の waveforms の例と同じですが、より複雑な物理チャネルのシミュレーションを示しています。

青い waveform は、受信機に到着する電圧が、以前に送信されたいくつかの bits の値を「記憶」している様子を示しています。前に説明したように、受信機は電圧が負か正かに応じて「0」または「1」を決定する必要があります。したがって、以前の bits の値は受信機の決定に干渉します。1 つの bitの値が別の bit に関する受信機の決定に干渉することを Inter-Symbol Interference (ISI) と呼びます。

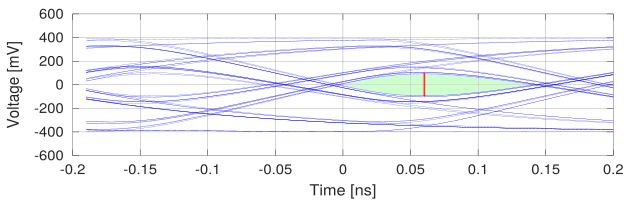

物理チャネルの同じシミュレーション用の eye diagram :

この eye diagram は、「0」と「1」を区別することはまだ可能ですが、その差ははるかに小さいことを示しています。言い換えれば、エラーを引き起こすのに必要なノイズははるかに少なくなります。

上記の eye diagram でシミュレートされた効果とは別に、信号は他の方法でも歪んでいます。

- 信号は受信機に伝わる途中でエネルギーを失うため、差動線間の電圧は送信された電圧よりも低くなります。

- 信号が送信機から受信機に伝わるときに、反射が加わります。この効果は音響エコーに似ており、特に信号がコネクタや伝導媒体の別の種類の突然の不連続性を通過するときに発生します。

- さまざまな外部ソースからのノイズが信号に追加されます。通常、歪みの影響の方が大きいため、これは MGTs間の通信では支配的な要因にはなりません。ただし、絶縁が不十分な長いケーブルでは、ノイズが大きくなる可能性があります。

ここでは、物理チャネルの信号歪みを軽減するための 2 つのメカニズムについて説明します。 受信機の一部である equalizerと、送信機の一部である pre-emphasis。

Equalizer

equalizer は、 MGTに届くアナログ信号を操作します。このユニットの目的は、物理チャネルの信号歪みの影響を軽減することです。これにより、 equalizer はチャネルのビット エラー確率を減らし、より高いデータ レートを実現します。 equalizer は常に Rx PMAの処理チェーンの最初のステップになります。

使用されている equalizers には主に 2 種類あります。 MGT は両方をサポートする場合があります。

- LPM (Low Power Mode)。この equalizer は通常、アナログ信号のスペクトルの高位部分を減衰させる物理チャネルの傾向を補正する high-pass filter で構成されます。一部の MGTs は、この filter を受信信号に自動的に適応させます。それほど高度ではない MGTsでは、 application logic は複数の可能性の中から 1 つの filter を選択する必要があります。

- DFE (Decision Feedback Equalizer)については、以下で詳しく説明します。

上記の例から、 Rx PMA は 2 つの input pins (D+ と D-) ) 間の電圧を 0.2 nsの期間ごとに 1 回測定することを思い出してください。この電圧が負か正かに基づいて、 Rx PMA は「0」または「1」を検出します。 equalizer が使用される場合、 Rx PMA は代わりに equalizer の output に依存します。

DFE を使用する場合、送信機は送信された bits が統計的に互いに独立していることを保証するものと想定されます。物理チャネルが信号を歪ませない場合はどうなるでしょうか。この場合、 Rx PMA が「0」または「1」を決定するために使用する電圧も、相互に統計的に独立しています。言い換えると、 Rx PMA が analog input signalを検査するたびに、以前の signals とも将来の signalsとも統計的な関係がないはずです。

しかし、実際には、物理チャネルはデータ ストリームを運ぶ信号を歪めます。したがって、「0」または「1」を表す電圧の間には統計的な関係があります。 low-pass filter 効果は電圧信号を不鮮明にし、反射 (「エコー」) も信号の品質を低下させます。各 bitの電圧レベルは隣接する bitsに波及します。前述のように、この効果は Inter-Symbol Interference (ISI) と呼ばれます。受信機が ISIの効果を軽減するために何も行わない場合は、 bits 間のこの相互干渉はチャネルにノイズを追加することと同等になります。

DFE は echo cancelerと同様に動作します。 これは、'0' または '1' を表す samples 間の correlation を除去するために調整する filter で構成されています。より正確には、検出された bits ('0' または '1') と隣接する bitsに属するアナログ信号との相関関係を除去します。言い換えると、 DFE が目的を達成した場合、 bitの値を決定するために使用されるアナログ信号と他の bitの値との間に統計的な相関関係はありません。この場合、 ISI はゼロに減少し、チャネルのスミア効果と反射が伝送品質に影響を与えないことを意味します。

チャネルで送信される bits 間に統計的な相関関係がある場合、 DFE はこの相関関係を排除しようとすることに注意してください。その結果、 DFE はアナログ filter を、物理チャネルのアナログ信号の歪みに対応しない方法で調整します。したがって、 DFE は信号を修復するのではなく、歪ませます。これが、 DFE がアクティブ化されるときに常に scrambler が必要な理由です。

送信された bits が相互に無相関であることを保証する方法がない場合は、 LPM equalizer が適している可能性があります。 MGTの datasheet は通常、 LPM equalizer を scramblerなしで使用できるかどうかを示します。

すべての MGTs に DFEがあるわけではありませんが、ほぼすべての MGTs に何らかの LPM equalizer があります。 datasheets の情報は、 MGT がサポートする equalizers の種類や、これらの equalizers の動作方法に関して不完全な場合がよくあります。 datasheet に equalizerの種類について何も記載されていない場合は、おそらく LPMです。

DFE は equalizerのより高度なタイプですが、 bits が相互に無相関であっても、 必ずしも LPMよりも優れたパフォーマンスを発揮するとは限りません。特に、物理チャネルの品質が比較的高い場合、 LPM は DFEよりも優れたパフォーマンスを発揮する可能性があります。

Pre-emphasis

送信機の output signal を操作して、受信機に到達する信号を改善すると役立つ場合があります。この方法は pre-emphasisと呼ばれ、信号の歪みがひどく、受信機がデータ ストリームでまったく同期できない場合に特に役立ちます。この方法にはいくつかのバリエーションがあり、各 MGT には独自の機能セットがあります。

ほとんどの場合、物理チャネルは low-pass filterの効果を持ちます。送信機は、送信機の output signalを整形することで、チャネルの歪みの一部を事前に補正できます。最も単純なメカニズムは post-cursor emphasisです。 物理チャネルは送信機の outputの変化にゆっくりと反応するため、送信機は bit が変化するとより高い電圧を適用してこれを補正します。より正確には、送信機は bit が変化しない場合に電圧を下げます。

このメカニズムを説明するために、上記の例では、送信機の output が -500 mV または 500 mV (「0」または「1」の場合) であったことを思い出してください。

post-cursor emphasisの場合、 output が「0」から「1」に変わると、送信機の output は以前と同じように 500 mV になります。ただし、次の bit が再び「1」の場合、出力電圧は 400 mVのように低くなります。「1」から「0」への遷移でも同じことが起こります。この場合、出力電圧は -500 mVになります。ただし、次の bit が再び「0」の場合、電圧は -400 mVになります。

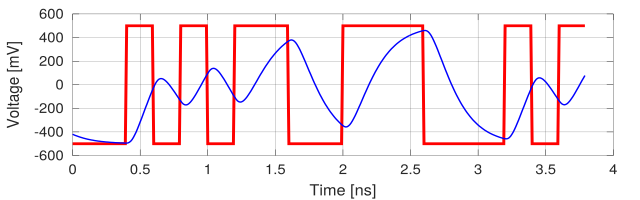

この画像は、 waveformsを使用した最後の画像と同じシミュレーションを示していますが、 post-cursor emphasis が適用されています。

赤い waveform は、 post-cursor emphasis がどのように動作するかを示しています。 出力電圧は、 bit が変化するたびにわずかにブーストされ、それ以外の場合は低い電圧に戻ります。この方法は、送信機が繰り返し bitsの電圧を下げるため、これらの bits は「あまり強調されない」ため、 de-emphasisと呼ばれることがよくあります。

青い waveform と上の画像を比較すると、この電圧の振幅が小さいことがわかります。これは大したことではないように思えるかもしれませんが、 eye diagramではその違いがより顕著です。

これは明らかに優れていますが、十分ではありません。 このようなシナリオでは、 equalizer が依然として必要です。

post-cursor emphasis は単純な FIR filterとして記述できることに注意してください。 emphasis のない送信機の電圧を x(n) と表します (n は送信される bit の数です)。各 x(n) は、値 -500 mV または 500 mVを持つことができます。したがって、 post-cursor emphasis のある送信機の output は次のように記述できます。

y(n) = 0.9 x(n) - 0.1 x(n-1)

これは、高周波信号に有利な FIR filter用のシンプルな expression です。これは、 low-pass filterとしての物理チャネルの動作を補正するものと見ることができます。

表現「post-cursor emphasis」の「post-cursor」の部分は、対応する FIR filter が次のように記述できるという事実に関係しています。

y(n) = (1-a) x(n) - a x(n-1)

この expressionでは、 a は通常、正の数として選択されます。

この FIR filter は基本的に次のことを言っています: y(n) の値は主に x(n)に依存しますが、 x(n-1) が同じ値だった場合、 y(n) はゼロに少し近くなります。 y(n)の操作は、前の bitに依存します。

したがって、「cursor」という語は現在送信されている bitに関連しています。「post」という語は、この filter が以前送信された bit、つまり「cursor」の後の bit に依存しているという事実を指します。

高周波信号に適した FIR filter の考え方を一般化することは可能です。特に、この FIR は MGTsに実装されることがよくあります。

y(n) = apre x(n+1) + a0 x(n) - apost x(n-1)

この expressionでは、 apost は既に提示されている post-cursor emphasis に関連しています。 apre は、「cursor」の前の bit 、つまり pre-cursor emphasisへの依存関係を表します。これは、 preshootとも呼ばれることがあります。これを、 FIR filterで表すことができる送信機の output signal の操作の全範囲をカバーする用語 pre-emphasisと混同しないでください。

各 MGT は、送信信号を整形するためのさまざまな可能性を提供します。 post-cursor emphasis は、複数の protocols で必要なため、通常は使用できます。その他のバリエーションについては、 MGTに依存します。

pre-emphasis の明らかな欠点は、送信機の調整結果が受信機にしか見えないことです。 equalizer は、最適な受信を実現するために継続的に調整できることを思い出してください。ただし、一般的に、 pre-emphasis のメカニズムは、信号が反対側でどの程度受信されているかを認識しません。これは、 protocolによって解決できます。たとえば、 Displayport protocol は、受信側が送信機に要求を送信できるメカニズムを指定します。このようにして、受信機は送信機の電圧レベルと post-cursor emphasisのレベルを制御します。

Pre-emphasis は、 physical channel が事前にわかっている場合、たとえば 2 つの FPGAs が PCB上で相互に接続されている場合にも便利です。ただし、特にデータ レートが高い場合 (8 Gb/s 以上) は、チャネルのパラメーターが不明な場合でも、 pre-emphasis を使用することをお勧めします。

pre-emphasis メカニズムと equalizer は、どちらも信号品質を改善し、エラーを削減する filters ですが、互いの代替品ではないことに注意してください。通常、これら 2 つのうちでは equalizer の方が強力なツールです。 pre-emphasisの役割は、 equalizer を支援すること、または受信機が送信機と同期できるほど信号品質が良好であることを確認することです。

Pre-emphasis は、多くのアプリケーションではまったく使用されません。このツールは、2 つの MGTs 間の距離が長い場合、特に信号が PCB上を移動する場合に便利です。距離が適度に短く、受信機に適切な equalizerが装備されている場合、通常、送信機の output signalを操作する理由はありません。

Statistical eye scan

すべてのデータがエラーなしで到着した場合でも、チャネルの品質を評価することが望まれることがよくあります。特に、チャネルがエラーを生成し始めるまでどのくらい時間がかかるかを知ることは興味深いことです。チャネルは堅牢ですか、それとも物理メディアにわずかな変更が加えられただけでエラーが始まりますか?

また、前のページで述べたように、チャネルが有用なデータの送信に使用されている場合、 BER テストを同時に実行することはできません。そのため、チャネル使用中の品質を評価することは困難です(すべてのエラーを報告する一部の protocols 、例えばxillyp2pを除く)。

リンクの品質を評価する一般的な方法は、受信機で eye diagram を測定することです。これは、信号がケーブルとコネクタで到着したときに実行できます。 この目的のための測定機器があります (かなり高価です)。ただし、信号が PCB を伝わって chip (特に FPGA ) に到達すると、通常、信号を受信する場所はありません。 probe を使用して PCB のワイヤに触れると、信号の形状が劇的に変化するため、測定は無意味になります。

この問題の優れた解決策は、 statistical eye scanです。これは、 Rx PMA 自体が signalの eye diagramを測定することを意味します。この方法には、いくつかの利点があります。

- signal は、 Rx PMA が「0」または「1」を決定するポイントで正確に測定されます。

- 測定によって signalは変化しません。

- 測定には equalizerの補正が含まれます。これにより、使用する equalizer の選択や、 parametersの微調整に役立ちます。

- CDR が送信機の clockの jitter に対応できない場合は、この測定でそれが確認できます。

- 測定は Rx PMAの通常の動作を妨げません。そのため、実際のデータを転送しながらチャネルをテストすることが可能です。

この方法には欠点が 1 つだけあります。 その結果は実際には eye diagramではありません。しかし、結果はほぼ同等に有用です。

前述のとおり、 Rx PMA は、到着信号の差動電圧が負か正かに基づいて、受信信号が「0」か「1」かを決定します。 CDR は、最適なタイミングでこの決定を行う役割を担います。

statistical eye scanの目的のために、「0」または「1」の決定を行う追加のユニットがあります。ただし、この 2 番目のユニットは、最初のユニットよりもわずかに早く、またはわずかに遅く決定を行います。この時間オフセットは、 MGTの registers を設定することによって制御されます (これは、 MGT が動作している間に実行できます)。

2 つのユニットのもう 1 つの違いは、信号が「0」であるか「1」であるかを判断する方法です。 すでに述べたように、最初のユニットは信号の電圧をゼロと比較します。2 番目のユニットは、代わりに他の電圧しきい値の範囲と比較できます。たとえば、電圧しきい値が 100 mVとして選択されている場合、2 番目のユニットは、受信信号が 100 mVを超える場合は「1」を決定します。それ以外の場合は、「0」を決定します。

したがって、2 番目のユニットは、時間と電圧の両方にオフセットがある以外は、最初のユニットとまったく同じことを行います。 MGT 内の logic は、指定された数の決定を自動的に比較し、決定が異なっていた回数をカウントします。言い換えると、この logic は、タイミングが移動され、しきい値電圧が移動された場合に、 bit 上の Rx PMAの決定が何回異なっていたかをカウントします。

これら 2 つのユニットの決定に違いがない場合、2 番目のユニットの位置 (時間と電圧で示される) が上記の eye diagrams で緑色にマークされた領域内にあることを意味します。この状況は、かなりの測定期間後にカウント結果がゼロになることで認識されます。2 番目のユニットの位置が緑色の領域の端に近づくにつれて、カウンターの結果はますます高くなります。

statistical eye scan は、時間オフセットと電圧しきい値の範囲で 2 つのユニット間のこの比較を繰り返すことによって得られます。これは、 application logic によって、または MGTの registers から JTAGを設定することによって行われます。このプロセスは、しきい値電圧の範囲で for-loop 内の時間オフセットの範囲で for-loop を実行するコンピュータ プログラムに似ています。この操作を完了するのにかかる時間は、測定の精度によって異なります。

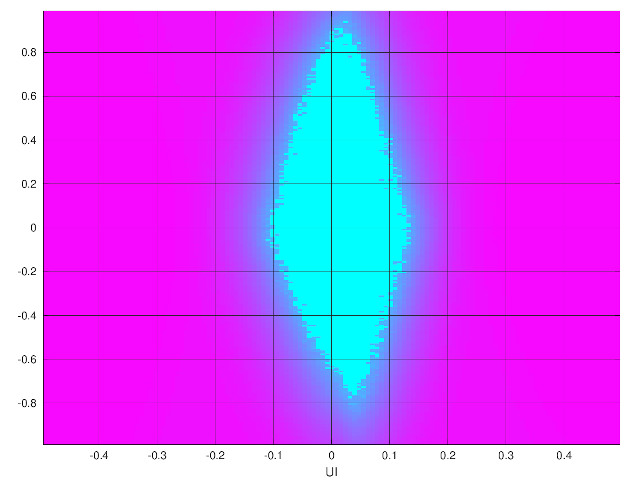

これは statistical eye scan ( 別のページから引用)を Artix-7 FPGAで測定した例です。中央の緑色の領域は、上記の eye diagrams の緑色の領域に対応しています。上記の例では1種類の信号歪みのみをシミュレートしたため、測定結果は上記のすべての画像とは定量的に異なります。

このような画像を取得するには約 1 分かかります。ただし、1 秒未満で取得できる粗い画像に基づいて、チャネルの品質を適切に評価することは可能です。

通常、 statistical eye scanを取得するために何かを設計する必要はありません。特に、このプロセスは、 JTAG 接続の助けを借りて Vivado によって実行できます。残念ながら、すべての MGTs が statistical eye scanの機能を備えているわけではありません。

これで、 MGTsに関するこのシリーズの 5 ページ目は終了です。次のページでは、引き続き PMA と、通常のデータ ストリームがオフになっている場合の機能について説明します。