このページは、 Multi-Gigabit Transceiver (MGT) を紹介する一連のページの最初のページであり、このシリーズの今後の予定の概要を示しています。

序章

Multi-Gigabit transceivers (MGTs) は、コンピュータまたは電子システム内の異なる部分間の通信で重要な役割を果たします。コンピュータ内のよく知られているインターフェイスのいくつかは、 PCIe や SATAなど、 MGTsに基づいています。その他のよく知られているインターフェイスは、コンピュータとその周辺機器間の通信に使用されます。たとえば、 Gigabit Ethernet、 SuperSpeed USB、 Thunderbolt 、 Displayportなどです。

MGTs は、電子部品間の接続にも使用されます。例えば、2つの FPGAs間などです。この場合、通信は、あまり知られていない protocols 、あるいは非標準の protocolに基づいて行われることが多いです。しかし、 MGTs は、 FPGA と別の種類の部品、あるいはXillyp2pなどの部品同士の接続にも使用できます。

例えば、光ファイバートランシーバーは、このサンプル設計に示すように、 MGTsと直接インターフェースする標準モジュール(特に SFP+ フォームファクター)であることが多い。一部の高速 ADC/DACs は、 sample data (通常は JESD204 protocolベース)を転送するために MGTs も使用する。一部の protocols はビデオデータの転送を目的としている(例えば、 MIPIの一部の protocols は物理層用である)。

MGTs は双方向の protocolsに使用されることが多いですが、各 MGT は実際には 2 つの独立した部分で構成されています。 送信機と受信機。したがって、2 つの部分のうちの 1 つをオフにすることで、 MGT を単方向送信に使用することができます。ほとんどの FPGA MGTsでは、送信機と受信機の parameters を個別に構成することもできます。

要約すると、 MGTs は多くのアプリケーションで使用されています。多くの場合、インターフェイスの名前は MGTs が使用されていることを意味しません (例: Gigabit Ethernet、 SATA 、 DisplayPort) が、物理層は MGTsで構成されています。

Xilinx (そして AMD) は MGTs を別の名前で呼んでいることに言及する価値があります。 RocketIO、 GTX、 GTH、 GTY、 GTP、 GTMなど。それぞれの名前はトランシーバーの特定のハードウェア実装を表しており、この名前はトランシーバーのデータ レートやその他のパフォーマンス属性について何かを示しています。

この一連のページでは、 MGTs の基本と、それに関連する一般的な技術用語をいくつか説明します。その目的は、技術文書を読みやすくし、特に、どのパラメータがプロジェクトに関連し、どのパラメータが関連しないかを認識できるようにすることです。

MGTとは何ですか?

複雑な機能の背後には、 MGT が単なる SERDESであることを認識することが重要です。 これは、データを送受信する電子ビルディング ブロックです。 MGTの物理世界との電気的インターフェイスは、差動ペアを構成する 2 本のワイヤで構成されています。最初のワイヤ (「プラス」または「正」ワイヤ) の電圧がもう一方のワイヤ (「マイナス」または「負」ワイヤ) の電圧よりも高い場合、物理状態は「1」に相当します。それ以外の場合は、「0」です。これは、 LVDSなどの差動インターフェイスと同じ原理です。

SERDES とのもう 1 つの類似点は、 MGTと application logic のインターフェースが並列ワードで構成されていることです。 application logicの clockの各サイクルでは、 application logic と MGTの間で多数の bits が送信されます。データ レートが FPGAで可能な最大 clock frequency よりもはるかに高いため、この配置が必要になります。

ただし、通常の SERDES と MGTの間には、いくつかの重要な違いがあります。そのいくつかを以下に示します。

- MGTs は、通常の SERDESよりもはるかに高いデータ レートを実現できます。

- SERDES の受信機には、データ ストリームとともに送信機の clock が提供される必要がある。一方、 MGT 受信機は、データ ストリームの signal のみに依存できます。 MGT は、データ ストリームの signal に一致する clock を作成し、代わりにこの clock を使用します。この機能はclock data recovery, CDRと呼ばれます。 MGT 受信機が送信機の clockにアクセスできる場合でも、 data clock 自体としてではなく、 reference clockとしてのみ使用されます。

- MGTを使用するデータリンクでは、Bit errors は許容され、正常です。 BER は通常、 10-12 または 10-15よりも低いと予想されます。通常の SERDESで bit error が発生した場合は故障とみなされますが、 MGTの場合はそうではありません。

- MGT を使用する場合、一対の電線で送信されるデータ ストリームの内容に制限があります。データ ストリームは常に DC バランスが取れている必要があります。言い換えると、データ ストリーム上の「0」と「1」の数は平均して等しくなければなりません。また、送信される bits は統計的に互いに独立していることが求められることもよくあります。これについては、以下で詳しく説明します。

- MGT は、 out-of-band signals (OOBs)を生成および検出できます。これらの signals は、エネルギーを節約するために通常のデータ フローがシャットダウンされたときに送信されます。これらの signals の主な目的は、 data bitsの送信を再開するために、反対側の受信機を起動することです。

では、 MGT はなぜそれほど複雑なのでしょうか?

FPGA プロジェクト用に MGT ブロックを設定しようとしたことがある人なら、パラメーターと選択肢がたくさんあることをご存知でしょう。なぜこのようにする必要があるのでしょうか?

実際のところ、複雑である必要はありません。 このサンプル設計で示されているように、 MGT を SERDESと同じように使用すると、複雑さが大幅に軽減されます。

ただし、 MGT の使用は通常複雑であり、主に次の 3 つの理由があります。 まず、 MGT ブロックは、 logic fabricで実装できる多くのビルディング ブロックを実装していますが、効率性のために MGT の一部として実装されています。たとえば、すべての MGTs には8b/10bをエンコードおよびデコードする機能がありますが、このタスクは application logicでも実行できます。ただし、このエンコード手法は非常に一般的に使用されているため、代わりに MGT がそれを処理する機能を備えています。

2番目の理由はclockingに関連しています。 MGTが正常に動作するためには、複数の clocks が必要です。さらに複雑なことに、 FPGAの logic fabricに使用される clocks と比較して、 clock(特にjitter ) の品質要件はより厳しくなっています。また、 SSC (Spread Spectrum Clocking) も使用される場合があり、事態はさらに複雑になります。

したがって、 clocking を正しく実行することは、 MGT 全般の正しいパラメータを選択することと同じくらい難しい場合があります。

3 つ目の理由は、 MGTs がいくつかの標準通信 protocolsをサポートするように設計されていることです。その結果、特定の protocol に必要な機能の名前は、多くの場合、 protocolの仕様から取得されます。このような専門用語は、関連する protocolを知らない人にはまったく意味がありません。このため、 FPGAの MGT ブロックを設定するときに、どの機能を有効にするかを決定することが難しくなります。

これらすべてのトピックについては、このシリーズの残りのページでさらに詳しく説明します。

知っておくべきこと

ほとんどのユースケースでは、 MGTs は、別の定評のある protocol、特に PCIeの物理層として使用されます。これらの状況では、 FPGA tools が詳細を処理するため、低レベルで何が起こっているかをあまり理解する必要はありません。

ただし、 application logic を MGTに直接接続する場合は、この logic が解決しなければならないいくつかの課題に注意することが重要です。これらの問題の一部は、 FPGAs間での使用を目的としたprotocols によって処理されます。

これは、考慮すべきトピックの短いリストです。これらのトピックのそれぞれについては、このシリーズの残りのページでさらに詳しく説明します。

- 単語の配置: 他の SERDESと同様に、 MGT はバイトまたはより大きなワードがどこから始まるかについての事前の知識を持っていません。 SERDESの場合、この問題は通常、到着するデータ ストリームが意味を成すまで、並列ワードを一度に 1 つの bit (bit slipping) ずつ移動することで解決されます。 MGTs に基づく Protocols は、通常、この目的のために同期ワードに依存します。

- 物理ワイヤ上の bits は DC バランスされている必要があります。最も簡単な解決策は 8b/10b エンコーディングを使用することですが、他の、場合によってはより適切な方法もあります。

- Scrambling: 受信側の MGTに equalizer を使用するのは、ほとんどの場合良い考えです。 equalizer は物理メディアの欠陥を補正し、それによって BERを減らします。これは、データ レートが高い場合、低コストのケーブルが使用されている場合、または物理的な距離が長い場合に特に当てはまります。ただし、一部の種類の equalizers では、送信されるデータが統計的にランダムである必要があります。 送信されたデータ ストリームでは、 bit と別の bit の間に相関関係は認められません。一般的な解決策は、ペイロード データと bitsの疑似ランダム シーケンスの間で XOR を実行する scramblerを使用することです。受信側は同じ疑似ランダム シーケンスで XOR を実行し、このようにして元のデータ ストリームを取得します。

- Bit errors: データは受信側の MGTにエラーとともに到着する場合があります。このデータを使用する logic は、このようなエラーに対処できるように設計する必要があります。一部のアプリケーションでは、エラーは無視できるほどまれであると見なされます (たとえば、生のビデオ データを送信していて、 BER が 10-15を下回っている場合など)。他のアプリケーションでは、データ リンクの信頼性を確保するために、エラー検出および/または再送信メカニズムが必要です。

- clock frequenciesの違い: MGT がデータ ストリームを受信すると、この signal は反対側の clock (つまり、送信機の clock) に基づきます。この clock は、受信機側で使用可能な clock と比較して、わずかに異なる frequency を持つ場合があります。ただし、 MGT と application logic 間のインターフェイスは、多くの場合、ローカル clockに基づきます。したがって、送信機の clock が受信機の clockよりも高速である場合、これは、 MGT が application logicにデータを配信できるよりも速くデータを受信することを意味します。その結果、この過剰なデータが MGT ブロック内に蓄積され、最終的に何らかの overflow が発生します。逆に、到着データ レートがローカル clockよりも低い場合、 MGT は各 clock cycleでデータを配信できません。これらの問題は、 reference clock がデータ ストリームとともに送信機から受信機に渡された場合でも発生します。 clockの frequency のわずかな変動は、この種の問題を引き起こすのに十分です。 protocol は通常、 idle wordsの助けを借りてこの問題を解決します。

- エネルギー消費量: MGTs は電力を大量に消費する傾向があります。これはデータ レートが高いことが一因で、高品質の PLLs は大量のエネルギーを浪費することがよくあります。したがって、 MGT は、たとえ非常に短い期間であっても、使用していないときはシャットダウンすることが望ましいことがよくあります。たとえば、 SuperSpeed USB リンクは、 50μsと同じくらい短い期間にデータが送信されていない場合、データ ストリームをオフにすることがよくあります。その後、必要に応じて OOB handshake を使用して操作を再開します。

PMA、 PCS 、 clocking

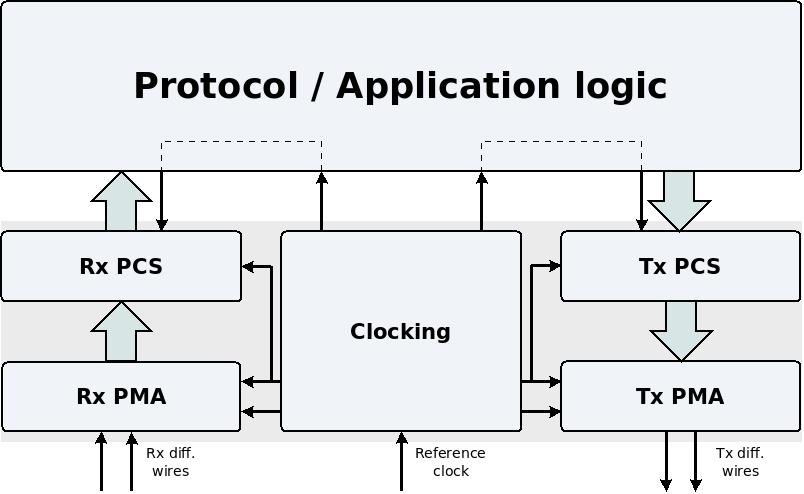

このブロック図は、 MGT の各部と application logicとの相互作用を示しています。

MGT の機能は通常、次の 3 つの部分に分かれています。

- Clocking : 前述のように、 MGTの動作には複数の clocksが必要です。 FPGA tools はこれらの clocksのパラメータを自動的に構成しますが、それでもこれらの clocks がどのように生成されるかを認識しておく必要があります。

- PMA (Physical Medium Attachment): この部分には、 MGTの SERDES とアナログ信号サブシステム (OOB signals、 receiver detection、 equalizer、 pre-emphasis など) が含まれています。この部分には、 CDRも実装されています。

- PCS (Physical Coding Sublayer): この部分には、通信 protocolの実装に役立つ logic が含まれています。 エンコーダーとデコーダー、ワード アライメント、 gearboxes、 FIFOsなど。 PCS の機能のほとんどは logic fabric に実装できますが、シンプルさと効率性のために MGT 内に実装されています。

これらのトピックについては、このシリーズのページでさらに詳しく説明します。

PIPE インターフェース

PIPE 規格は注目に値します: この規格は、 PCIe、 SuperSpeed USB 、または SATAを実装する MGT と logic 間の接続を定義します。これには、データ、制御信号、およびステータス信号の通信に使用される ports が含まれます。

この標準では、 MGT は PHY 層、 protocol は MAC 層と呼ばれます。この用語は、 Ethernet、 USB 1.x 、 USB 2.0を定義する標準でも使用されています。これらの標準は通常、2 つの別個の chipsによって実装されます。たとえば、 Ethernet を processor chipに実装するには、 MAC 層をこの chipに実装し、 PHY 層を別の chipに実装します。 PIPE 標準は、 PCIe、 SuperSpeed USB 、または SATA が実質的に常に同じ chipに完全に実装されているにもかかわらず、同じ精神で記述されています。 PIPE 標準で定義されている MAC 層と PHY 層間の接続は、 chip内で行われ、外部から見えることはほとんどありません。

PIPE 標準の重要な影響は、適切な FPGA MGT が常に PCIeに必要な PIPE インターフェイスを実装していることです。 SATA の PIPE インターフェイスもサポートされることがよくあります。これは明らかに、これら 2 つの protocolsを実装するときに役立ちますが、もう 1 つ重要な利点があります。 さまざまな FPGAs には、 MGTと同様のインターフェースがあります。特に、実質的にすべての MGTsに共通する機能要素がいくつかあります。

結論

このページでは、 MGT の概要とその複雑さについて説明しました。このシリーズのページの残りの部分では、上記の概念の多くについて説明します。しかし、その前に、2 つの FPGA MGTsを接続するときによく使用される protocols の簡単な概要から始めましょう。