このページは、 Multi-Gigabit Transceiver (MGT) を紹介する一連のページの 7 番目です。

序章

FPGAの MGT を構成する作業のほとんどは、データの処理と適切な protocolの選択に関連すると予想するのは当然です。したがって、 clocking を正しく構成するには、どれだけの時間と労力が必要であるかは、驚くかもしれません。この労力のほとんどは、通常、 MGT が clock resources に関連して提供するさまざまなオプションと、それらが課す制限を整理することに費やされます。

MGTの clocks に関連する設計ルールは各 FPGAごとに異なるため、このトピックに関する正確で包括的な情報の唯一の信頼できるソースは、 MGT自体のドキュメントです。このようなドキュメントは通常、メカニズムとその詳細に焦点を当てており、これらのメカニズムが必要な理由については説明されていない可能性があります。このページでは、 MGTで使用される clocks に関連する概念と課題について説明することで、このギャップを埋めようとしています。

PLLs および VCOs

一般的に言えば、 PLLs は reference clock の frequency を定数で乗算します。この定数は整数の場合もありますが、小数の場合もあり、1 より小さい場合もあります。つまり、 PLLの output の frequency は、 reference clockの frequencyよりも低くなる可能性があります。これは、 MGTsで使用される PLLs ではほとんど起こらない状況ですが、 logic fabricの PLLs では役立つ場合があります。

FPGAには、 MGTsに必要な clocks を生成するための別の PLLs があります。 logic fabric に属する PLLs およびその他の clock resources は、 MGTに必要な frequencies をサポートできません。特に、 MGT には、 frequency が少なくともデータ レートの半分である clock が必要です。データ レートが低い場合、必要な frequency は高くなる可能性があります。

たとえば、データレートが 5 Gb/sの場合、 bit clock は通常 2.5 GHzで動作します。これは、 MGTの SERDES が clock edges (DDR)の両方でアクティブ化されるためです。ただし、データレートが比較的低い場合は、 MGTの PLL の output が、より低い frequencyに分割されることがあります。

ほぼすべての PLLs は同じ原理に従って動作します。 中央部分は、 frequenciesの範囲を持つ clock を生成できる VCO (Voltage Controlled Oscillator)です。 VCOの output は、 frequency を定数で割る clock divider に挿入されます。 clock divider の output は、 PLLの reference clockと比較されます。制御メカニズムは、 reference clock と clock dividerの output が揃うように、 VCOの frequency を調整します。言い換えると、これら2つの signals は同じ frequency と同じ phaseを持っています。

5 Gb/sの例に戻って、 reference clockの frequency が 125 MHzであると仮定します。 PLL の可能な実装は、 VCOの output を 20で割ることです。割った signal は reference clockと比較され、整列されます。したがって、 VCOの frequency は 2500 MHz / 20 = 125 MHzであるため、 2500 MHzである必要があります。

clock を作成するこの方法は、 bitsの送信に適しています。 送信側の MGT は、各 bitの期間の開始と終了を独自に決定します。ただし、 MGT が bitsを受信すると、相手側が各 bitのタイミングを決定します。したがって、受信側は到着するデータ ストリームに適応する必要があります。前のページの 1 つで述べたように、この適応メカニズムは Clock Data Recovery (CDR) と呼ばれます。 CDR の実装は、受信側の clock を到着するデータ ストリームに同期させるために VCOの frequency を調整する control loop で構成されます。 reference clock は、予想される frequencyに十分近い初期 frequency に VCO を配置するために時々使用されます。同期が達成されると、 reference clock は無視されます。

PLLsの活用

FPGA 内の MGTs の PLLs は複雑なトピックです。各 MGT は、複数の PLLから clock を受け取ることができます。 FPGA プロジェクトで MGTs を使用するアプリケーションが 1 つしかない場合、 tools は通常、最も適切な PLL を自動的に選択します。ただし、プロジェクトで MGTs が異なる目的で使用される場合は、各 MGT が最も適切な PLL に接続されていることを確認することが重要です。

FPGAでは、通常、複数の MGTsで共有される PLLs があります。 AMD (Xilinx) はこれらを QPLLと呼び、 Altera には fPLL と ATX PLLがあります。一方、特定の MGTにローカルな PLLs があります。これらは CPLL (AMD / Xilinx) または CMU PLL (Altera) と呼ばれます。ローカル PLLs は通常、共有 PLLsと比較して品質が低く、機能も少なくなります。違いは、 frequencies、 jitterの範囲、および reference clockに関連して選択できる乗算比です。

各 FPGA には、 PLLs と MGTs を相互接続する方法を定義する一連の複雑なルールがあります。これらのルールは、 PLLs を FPGAの reference clock inputsに接続する可能性も定義します。したがって、すべての MGTs が必要な clocks に接続できることを当然と考えることはできません。これは、ほとんど制限がない logic fabricの clocksとは大きく異なります。

したがって、各 MGTにどの PLL を選択するかを決定する前に、 datasheet を注意深く読むことをお勧めします。特に、 PCBを設計するときに、すべての MGTs に clocks を提供できることを確認することが重要です。これは、必要なすべての MGTsを含む FPGA プロジェクトを作成し、このプロジェクトの implementation が成功し、すべての pins が正しい位置に配置されていることを確認することで実行できます。

Reference clock

FPGA には、 MGTsの PLLs用に設計された reference clocks 用の別の pins があります。 PCB designでは、 clock が対象とする MGTs で reference clock input を使用できることを確認することが重要です。 reference clock inputs、 PLLs 、 MGTs 間の相互接続では、すべての可能な組み合わせが許可されているわけではありません。許可されている組み合わせは FPGAのドキュメントに記載されていますが、ルールが複雑な場合があるため、最終的な結論に達するのは難しい場合があります。多くの場合、 FPGA プロジェクトの助けを借りてニーズが満たされていることを確認する方がよいでしょう。

この目的で使用される clocks は、精度の点で高品質で、 jitterが低い必要があります。汎用 clock chipによって生成された clock を接続するのはよくある間違いです。これを行うと、 MGTのパフォーマンスが低下し、信号整合性の問題やデータ ワイヤ上のノイズの増加のような障害が発生する可能性があります。

MGT が特定の protocol (例: PCIe、 SuperSpeed USB 、または SATA) 用である場合は、 reference clockの要件に関する FPGA メーカーのドキュメントを読むことをお勧めします。「low-jitter clock source」というラベルが付いている電子部品の中には、十分ではないものもあります。

Jitter はランダムなプロセスです。 jitterの大きさは重要なパラメータですが、必ずしも十分なものではありません。 clockの jitter のランダム性により、 clock cycleに急速な変化が生じる場合もあれば、ゆっくりとした変化が生じる場合もあります。この点で jitter がどのように動作するかは、 jitterの noise spectrumから推測できます。

clock を作成するコンポーネントの datasheet は、 jitter の大きさの数値 (通常は picosecondsで測定) のみを示す場合があります。 jitterの noise spectrum に関する情報は、多くの場合入手できません。特に jitterの大きさがとにかく非常に低い場合、このようなコンポーネントは、この情報の欠如にもかかわらず適切である可能性があります。この質問に対する簡単な答えがないことがよくあります。

それでも、 reference clockの品質は、 MGTのあらゆる用途にとって重要です。よく知られている protocolsの要件は、あらゆるプロジェクトで使用できる優れたリファレンスです。また、 development boardsで reference clocks として使用されるコンポーネントと比較することも役立ちます。

logic fabric用のClocks

MGT と logic fabric 間のインターフェースに使用される clock は、 MGT自身の PLLから派生したものです。これは、 PMA 内部で SERDES が 2 つの clocksに依存しているために必要です。 物理チャネル上の bits に対応する clock と、パラレル ワードとともに使用される clock 。 SERDES が適切に動作するには、これら 2 つの clocks が PMA内で整列している必要があります。

一方、 logic fabric によって使用される clock は、 clock skewが低くなるように分散される必要があります。この目的のために、 tools は global clock buffer を選択することがよくあります。 clock buffer からすべての logic elements への propagation delay はほぼ等しいため、 clockの edges はすべての宛先に同時に到着します。これは、 tools が logic fabricに関して適切な timing 計算を実行できるようにするための必要条件です。

この propagation delay はすべての wiresにわたって均一ですが、必ずしも小さいわけではありません。逆に、 clock buffer をその宛先に接続する FPGA 内の wires は、かなりの delayを追加します。これらすべての接続間の違いは小さいため、これは通常問題になりません。

しかし、この delay により、 PMA が使用する 2 つの clocks が logic fabricの clockと整列しなくなります。 logic fabricのリソースを利用してこれら 3 つの clocks を整列させることは不可能です。これは、これらの clocks の 1 つに高すぎる frequency があるためです。さらに、 MGT と logic fabric には、両側が同期する clock が必要です。唯一の解決策は、別の clock signalを追加することです。

つまり、各方向に少なくとも 3 つの clock signals が関与している必要があるということです。

- 物理チャネル上の bits と同期している clock 。この clockの frequency は、多くの場合、データ レートの半分になります (上記の例では2.5 GHz )。

- PMA内のパラレル ワードと同期する clock 。この clock は、 XCLKと呼ばれることもあります。たとえば、 PMA が 32 bits 幅のパラレル ワードで PCS とインターフェイスする場合、この clock は 156.25 MHz です ( 5000 / 32 = 156.25であるため)。

- logic fabricの clock: これは、 MGT と logic fabric間のインターフェイスとともに使用される clock です。この clock には通常、 TXUSRCLK2、 RXUSRCLK2、 tx_coreclkin、 rx_coreclkin などの名前が付けられています (下の図の「Tx user clock」および「Rx user clock」)。この clockの frequency は、 logic fabricとのインターフェイスに使用されるパラレル ワードの幅によって異なります。

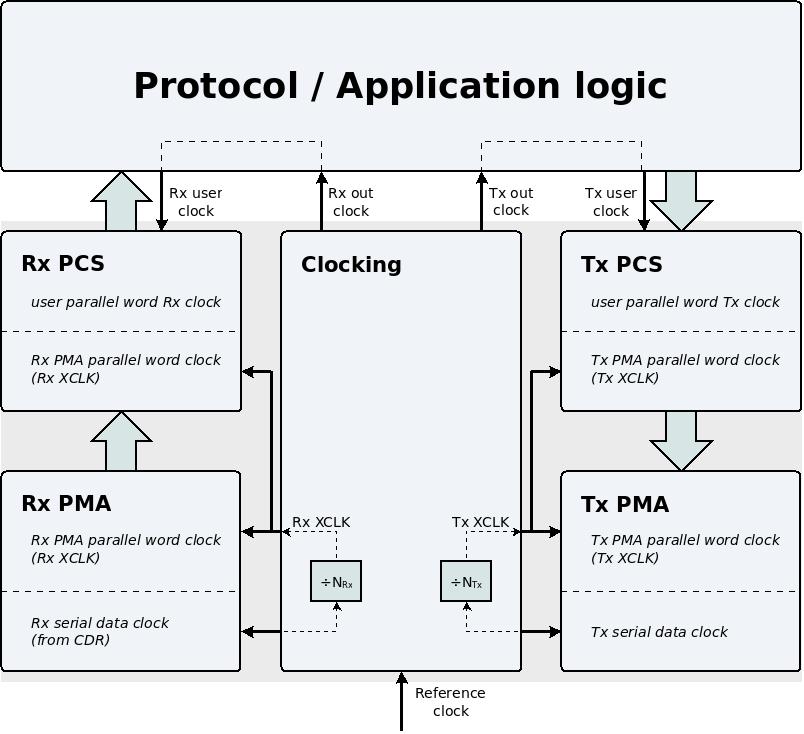

一般的に、送信用と受信用に別々の clocks があることに注意してください。このブロック図は、 MGT内の clocks の一般的な分布を示しています。

このブロック図では、各方向に clocks が 3 つではなく 4 つあります。これについては次に説明します。

logic fabricの clockの生成

上で説明したように、 logic fabric と MGT に共通する clock は、 logic fabricの clock bufferとともに配布される必要があります。一方、この clock は、 MGTの内部から発生するはずです。

まず、これら 2 つの矛盾する要件に対する最も単純な解決策から始めましょう。 MGT は実際に clock を生成し、 output portで使用できるようにします。この output port は通常、 TXOUTCLK、 RXOUTCLK、 tx_clkout、 rx_clkout などと呼ばれます (これは、上の図で「Tx out clock」および「Rx out clock」と名付けられた 4 番目の clockです)。この signal は、 logic fabric clock bufferの input に入ります。この clock buffer の output は、 MGT と logic fabric間のインターフェイスに使用される clock signal です。

この配置の結果、 logic fabricの clock と MGT によって生成された clock の唯一の違いは、 clock bufferの propagation delay です。言い換えると、 MGT は、 phaseを除いて、 logic fabricの clockを完全に制御できます。これは、 CDRの clock が logic fabric とのインターフェイスのベースとして使用される場合 (このオプションについては後述)、特にデータを受信する場合に重要です。これは、 CDR が、到着するデータ ストリームとの同期を維持するために、この clockの frequency を継続的に調整するためです。

前のページで説明したように、 PCS は、 logic fabricの clock と PMAの clockの phases の違いを克服するためのメカニズムを提供します。 Tx buffer または Rx buffer が最も簡単な選択ですが、 PCS にもこの違いを直接調整する機能がある可能性があります。

しかし、 MGTの clock output portで公開される clock はどれでしょうか? 自然な答えは XCLKです。この clock が logic fabricの clockの要件に最も近い候補だからです。ただし、 logic fabricの clockを生成する方法は他にもいくつかあります。たとえば、 MGTの clock output を通常の logic fabric PLL に入力して、異なる frequencyを持つ clock を生成できます。この PLL は clock bufferと一緒に使用されるため、 clock signal で十分です。このように PLL を使用すると、たとえば MGT が clock output portで独自の reference clock を通過するなど、新しい可能性が開かれます。この clock の frequency は、 MGTとのインターフェースに clock を使用するには正しくない可能性がありますが、 PLL は、この clock を必要な比率で乗算できます。

また、 logic fabricの clock の frequency は、 XCLKの frequencyと異なる場合があることに注意してください。これは、 PCS内で asynchronous gearbox がアクティブ化されるときに必要になることがあります。このシナリオでは、 PMA と logic fabricとのインターフェイスの並列ワードの異なる幅を補正するために、 frequency の差が必要になります。

このトピックに関連するルールは複雑で、 FPGA ごとに異なります。 MGTのドキュメントの大部分は、さまざまな可能性の詳細を説明することに費やされることがよくあります。残念ながら、 clocking で正しい決定を下すには、特定の FPGAに適用されるルールを学習するのに時間を費やす必要があります。

データ受信には logic fabric clock を選択

データの受信を目的とした logic fabricの clock を生成する方法を選択する際には、基本的な決定が必要です。 この clock が CDRの clock から派生したものか、固定の reference clockから派生したものか。言い換えると、 logic fabricの clock が到着するデータ ストリームの正確なデータ レートに適合されているかどうかです。

ほとんどのアプリケーションでは、 MGT は双方向のデータ通信に使用されます。到着データと送信データの間には密接な関係があることがよくあります。たとえば、送信データ ストリームには、到着データ ストリームへの応答として送信される確認応答や再送信要求が含まれる場合があります。この種のアプリケーションでは、すべての logic が同じ clock と同期している (つまり、すべての logic が同じclock domainにある) と便利です。特に、 PIPE インターフェイスでは、 MGT とのすべてのインターフェイスが単一の clock (標準ドキュメントでは PCLK と名付けられています) と同期している必要があります。前述のように、 PIPE は MGTs と複数の protocols間の標準インターフェイスです。 PCIe、 SuperSpeed USB 、 SATA。

ただし、この利便性には代償が伴います。 logic fabricの clock の frequency は、 PMAのパラレル ワード (つまり、 XCLKの frequency) で使用される frequency とはわずかに異なる可能性があります。この違いにより、 logic fabric がパラレル ワードを受信する速度が、これらのワードが PMAに到着する速度よりも遅いか速いため、 PCS内でデータの過剰または不足が発生します。この問題の解決策は、多くの場合、 PCSのページで説明されているように、 Rx buffer と skip symbolsを使用することです。

あるいは、 logic fabricの clock を PMAの clockから派生させることもできます。この方法では、 logic fabric は到着したデータと同じ速度でデータを消費します。これは、 MGT をデータ受信のみに使用する場合の自然な解決策です。また、アプリケーション logic が clock domain crossingを処理する場合の双方向リンクにも適用できます。Xillyp2pは、このアプローチを採用した protocol の一例であり、その完全な設計例をご覧ください。

AMD FPGA: logic fabricの2台の clocks

AMD FPGAs (以前の Xilinx) 上のMGTs には、 logic fabricからの 2 つの clock input ports 、つまり各方向に 2 つの ports があります。 送信用には TXUSRCLK と TXUSRCLK2 、受信用には RXUSRCLK と RXUSRCLK2 を使用します。この設計例では、 MGT の instantiation の例を示します。

logic fabric とのほぼすべてのインターフェイスは、 TXUSRCLK2 または RXUSRCLK2 (方向によって異なります) と同期しています。他の 2 つの inputs、 TXUSRCLK 、および RXUSRCLK は、 PCSの一部の内部でのみ使用されます。

TXUSRCLK は、多くの場合、 TXUSRCLK2と同じ clock signal です。ただし、 AMDの FPGAs の MGTs には、 logic fabric とのインターフェイスで使用される並列ワードを PCS内の 2 倍の幅にできる機能があります。この機能を使用すると、 TXUSRCLKの frequency は、 TXUSRCLK2の frequency の 2 倍になります。これは、 logic fabric PLLを使用するもう 1 つの理由です。

RXUSRCLK および RXUSRCLK2にも同じ原則が適用されます。

概要

このページでは、 MGTの clocksに関連するいくつかのトピックを簡単に取り上げました。それでも、 MGTの clocking resourcesの利用について賢明な決定を下すには、 MGTの特定の機能と制限について理解する必要があります。このページの説明が、 MGTの clocks がどのように動作し、相互に作用するのかを理解するのに役立つことを願っています。

MGTsに関するシリーズの7ページ目はこれで終わりです。次のページでは flow controlについて考察し、シリーズを締めくくります。