序章

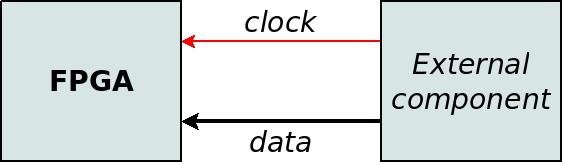

このページでは、 source-synchronous data inputsについて説明します。 この手法は、 data inputs が、これらの inputsと並行して外部コンポーネントが生成する clock と同期していることを意味します。

このメソッドは、外部コンポーネントが動作する方法であるため、よく使用されます。もう 1 つの正当な理由は、 data のソースが FPGAから物理的に離れていることです。 FPGA と反対側の間にケーブルとコネクタがある可能性もあります。たとえば、 pixel dataを送信する digital camera 。

source-synchronous clock で考えられる問題は、常にアクティブであるとは限らないことです。 clock signal は、ぶら下がっている物理的な接続や過度のノイズの影響を受ける場合もあります。 clock に安定した clock periodがないか、 jitter が高すぎる可能性もあります。これは、 data (したがって clockも) のソースが microprocessorの I/O peripheralである場合によく発生します。

clock と data の一般的な関係を説明する別のページがあることに注意してください。

不安定な clockへの対処

source-synchronous inputs に関する最も重要なガイドラインは、 clock を FPGA内の logic elements に直接接続しないことです。むしろ、 FPGA 内で使用される clock は、 FPGA内の PLL によって生成されるクリーンな clockでなければなりません。

外部 clock が FPGA内の logic に直接接続されている場合、奇妙な問題が発生する可能性があります。 clock の不具合により、 clockでは問題にならないような予期しない動作が発生します。 jitter と glitches が過剰になると、 designの信頼性の高い動作を保証する timing の要件に違反する可能性があります。その結果、 Verilog codeでは不可能な状況も含め、事実上あらゆることが発生する可能性があります。そのため、 FPGA designの bug に問題があると誤解しがちです。

clock の問題は clock cyclesの損失のみを引き起こし、その結果 data 要素の一部が失われると (誤って) 考えるのは自然なことです。不良 clock が他の問題を引き起こす場合、この問題を解決しようとする試みは、多くの場合、 logic design の最も関連性が高いと思われる部分に集中します。それは多くの時間を無駄にする可能性があります。

外部 clock を logic fabric で直接使用できる唯一の状況は、この clock が安定してクリーンであることが保証されている場合です。 FPGA が動作を開始したときにこの clock が安定していない場合、この問題には次の処理が必要です。 clock が不安定である限り、この clockに依存する logic に reset を適用する必要があります。

考えられる戦略

外部 clockとの同期には、主に 4 つの方法があります。これらの戦略については、順不同で以下に説明します。

戦略 1: 01-signal sampling

この戦略は、 source-synchronous inputsにとって最も堅牢な方法です。外部の clock が誤動作している場合、 01-signal sampling は他のどの方法よりも明らかに有利です。ただし、この方法は、データ ソースの clock の周波数が比較的低い場合にのみ役立ちます。

この方法については、専用ページで別途説明します。

戦略 2: PLLの使用

この戦略では、外部 clock は FPGA上の PLL の input に接続されます。この PLLの output clock を logic elementsに使用しています。 PLL がロックされていない場合、これらの logic elements に reset signal が適用されます。このソリューションにより、 logic elements が安定した clockに依存することが保証されます。 PLLの output clock が安定していない場合、 logic elements は resetによって非アクティブ化されます。

PLL を使用すると、外部の clock を直接接続する場合と比べて、 timing constraintsの実現が容易になります。 PLL は、 clock pin と FPGAの内部 clockの間で delay を補正します。

ただし、外部 clock の不完全性により、 PLLの outputで過剰な jitter が発生する可能性があることに注意してください。 PLLの lock detector は、それが生成する clock が異常にノイズが多い場合でも、 PLL が正常に動作していることを示し続ける場合があります。この状況に対する簡単な解決策はありません。 1 つの可能性は、 PLLの outputに依存する logic をtiming constraintsに変更することです。たとえば、 timing constraints の clockの jitter は、 PLL がおそらく超えない値まで増やすことができます ( loss of lock が発生するため)。

この戦略とsystem synchronous clockingには類似点があります。 どちらのシナリオでも、外部 clock は PLLに接続され、この PLL の output は FPGA内で使用されます。したがって、 timing constraints はsystem synchronous clockと同じ方法で記述されます。

PLL は通常、 system synchronous clockに最適な方法で output clock を external clock と整列させることに注意してください。 source synchronous clock の最適な位置合わせは、若干異なる場合があります。どちらの可能性においても、 clocks は完全には一致していません。むしろ、 clocksと edgesの間に意図的にわずかな時間差があります。この時間差により、 I/O registersの timing 要件を満たすことが容易になります。一部の PLLs は、 source synchronous clockで最適なパフォーマンスを得るために clocks を調整するように構成できます。

この戦略は、ここにリストされている他の戦略と比較して、最も簡単に実装できます。比較的高い clock 周波数に適しています。しかし、 I/O の能力の最大値に近い周波数では、この戦略はおそらく機能しません。

戦略 3: Phase shifting

この戦略は通常、 data rate が FPGA がサポートできる最大値に近い場合に選択されます。

timing requirements を保証する通常の方法は、このような data ratesでは機能しません。 timing constraintsを達成することは不可能でしょう。ただし、 data signals の信頼できるサンプリングは引き続き可能です。

timing constraintsの問題は、計算を通じて timing requirements を確実にすることです。 このような計算には、 FPGAの製造上の違いなど、いくつかの不確実なパラメータが含まれます。これらのパラメータを考慮すると、信頼できるサンプリングを保証する timing ソリューションが計算で得られません。 data rate が非常に高い場合、これらの不確実性のために無駄にする timing の余剰はありません。

しかし、特定の FPGA chipの場合、これらのパラメータは一定です。したがって、解決策は、 FPGA が動作している間に正しい timing を検索することです。実際には、これは、 FPGA 内の state machine が data clock と samplingの瞬間の間で delay を調整することを意味します。したがって、計算に頼るのではなく、適応メカニズムを使用して最適な timingを見つけます。このメカニズムはphase shiftingと呼ばれます。

この戦略は、 DDR SDRAM memoriesから data signals によく使用されます。このアプリケーションでは、目標は常に data rate を可能な限り高くすることです。したがって、 I/O portsの機能は限界まで押し上げられます。したがって、 phase shifting は、 data inputs が確実にサンプリングされることを保証する唯一の方法です。 DDR memory が初期化された後、 data の特別なシーケンスが memory に書き込まれます ( data signals から memory はsource-synchronous outputsであるため、 timingに問題はありません)。 FPGA は、 DDR memoryの同じ部分から繰り返し読み取ります。 state machine は、サンプリングの delay を徐々に変更することにより、最適な timing を見つけます。予想される input data は既知です。これは、以前に書き込まれた data のシーケンスと同じであるためです。したがって、 state machine は data の信頼性を簡単に評価し、最適な delayを見つけることができます。

このメカニズムの興味深い特徴は、 DDR chip によって提供される data clock を無視できることです。 DDR memory は、 FPGA が生成する clock と同期されます。この clock は、 DDR memoryが受け取るsource-synchronous outputsの一部です。したがって、 source-synchronous inputs の data clock は、 FPGAによって生成される clock とまったく同じ周波数を持つことが保証されています。したがって、 phase shifting メカニズムは、 dataとともに到着する clock ではなく、内部 clock に依存できます。これら 2 つの clocksの間に未知の delay があっても問題ありません。 state machine は、この delayに関係なく、最適な timing を見つけます。

実際、 DDR memoriesでは通常、このメカニズムが次のように実装されます。 DDR memories には source-synchronous clock ( data strobeと呼ばれる) がありますが、 phase shifting メカニズムの通常の実装では、この signalは無視されます。その根拠は、 strobeと連携するよりも、 data signals が確実に到着することを保証することの方が重要であるということです。

したがって、 phase shifting を使用すると、 data clockが不要になります。周波数が data rateとまったく同じであることが保証されている場合は、代わりに内蔵 clock を使用できます。

この戦略では、 timing constraints の目的は通常の IOB registersと同じです。

戦略 4: clock を直接使用する

この戦略は明らかに最も単純なものです。 外部 clock は、 FPGA内部の flip-flops に直接接続されます。このようなもの:

module top (

input data_clk,

input [7:0] data

);

reg [7:0] data_samp;

always @(posedge data_clk)

begin

data_samp <= data;

[ ... ]

end

前述のように、この戦略は通常はお勧めできません。主な理由は、 @data_clk に glitchがある場合、この clock に依存するすべての logic が予測不能になることです。

クリーンかつ安定していることが保証されている場合、外部 clock をこのように使用することは合理的です。ただし、これが保証されている場合でも、 clock pin と flip-flopsの間に delay があるため、 timing requirements を達成するのは難しい場合があります。一部の FPGAs には、この delayを削減する目的で特別な clock resources があります。このためには、専用の clock input pin を使用し、 I/O ports を FPGAの特定の領域に制限する必要がある場合があります。

clock を直接使用する場合、 timing constraints はsystem synchronous clockと同じ方法で記述されます。

この戦略の直接的な代替手段は、上記で提案したように PLLを使用することです。 data clock が安定していない場合は、 01-signal sampling を検討する必要があります。

概要

01-signal sampling がこのページで最初に言及され、この戦略が別のページで説明されているのは偶然ではありません。 これは、 data rate がこの方法よりも高くない場合に最も推奨される方法です。

他の戦略を検討する場合、 data clockの安定性に注意を払うことが重要です。 clock が許容される動作 (つまり、 clock period と最大の jitter) から逸脱した場合、関連する logicの永続的かつ回復不能な誤動作が発生する可能性があります。 reset のみが logic を通常の動作に戻します。

信頼できる clock を生成するために PLL を使用すると、状況が大幅に改善されます。 PLLの output は、 lock detector が示す限り信頼できます。それ以外の場合は、この logic に reset を適用する必要があります。