序章

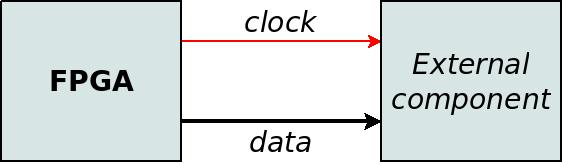

このページでは、 source-synchronous data outputsについて説明します。この手法は、 data outputs が、これらの outputsと並行して FPGA が生成する clock と同期していることを意味します。

外部コンポーネントとのインターフェースが FPGAから output ports のみで構成されている場合、このアプローチは当然の選択です。このページの下部で説明されているように、 I/O が双方向の場合にも適しています。 clock と data の一般的な関係を説明する別のページもあります。

基本的なアプリケーション

この Verilog の例を考えてみましょう:

module top (

input clk,

output reg [7:0] data_out,

output reg sync_clk_out

);

always @(posedge clk)

begin

sync_clk_out <= !sync_clk_out;

if (sync_clk_out)

data_out <= data_out + 1;

end

endmodule

@data_out は @sync_clk_outの falling edgeと同時に値を変更することに注意してください。 @sync_clk_out が Low の場合、 @data_out は変化しません。 @sync_clk_out が High の場合、 @clkの rising edgeに応答して @data_out が新しい値に変化します。

IOB registersが @data_out と @sync_clk_outの両方に使用される場合、これらの output signals はすべて実質的に同時に値を変更します。したがって、これらの signals を受信する外部コンポーネントは、 @sync_clk_out を clockとして使用できます。通常、この方法では外部コンポーネントの timing 要件を満たすのは簡単です ( @data_out の sampling が @sync_clk_outの rising edgeと同期されていると仮定)。

DDR registersの使用

上記の例には重大な欠点があります。 @sync_clk_out の frequency は、 @clkの frequency の半分です。したがって、 @data_out の data rate も @clk の frequency の半分に制限されます。唯一の例外は、外部コンポーネントが @sync_clk_outと clock edges の両方に敏感な場合 (つまり、 DDR inputがある場合) です。通常はそうではありません。

data outputsと整合する output clock を生成するために、 output DDR register を使用することができます。アイデアは、両方の clock edgesで値を変更する flip-flop を使用することです。したがって、そのような flip-flop は次のように動作します。

always @(posedge clk or negedge clk)

if (clk)

sync_clk_out <= 0;

else

sync_clk_out <= 1;

@sync_clk_out は、 @clkの rising edge に応じて低くなります。 falling edgeにより逆のことが起こります。結果は、同じ frequencyを持つ output clock になります。

ただし、この Verilog code はほとんどの synthesizersでは動作しません。これは、 logic fabric の flip-flops が通常、両方の clock edgesを感知できないためです。この機能があるのは IOB registers のみで、 synthesizer がこの可能性を理解できるほど賢いことはめったにありません。

したがって、 logic primitive の instantiation が必要です。 primitive は、使用されている FPGA に固有のものです。この例は、 Kintex Ultrascaleでこれを行う方法を示しています。

ODDRE1 ODDR_ins

(.C(clk), .Q(sync_clk_out),

.D1(1'b0), .D2(1'b1),

.SR(1'b0));

しかし現在、 clock は output DDR register で生成され、 data signals は通常の IOB registersで生成されています。 data と clock の間の調整は、以前ほど明白ではありません。したがって、すべての outputsについて timing reports を読み取り、 delays 間の差が十分に小さいことを確認することが重要です。

data に output DDR registers を使用することもできます。 D1 と D2に同じ値を指定すると、 output は clock cycleごとに 1 回だけ変更されます。

module top (

input clk,

output [7:0] data_out,

output sync_clk_out

);

reg [7:0] data;

ODDRE1 ODDR_ins

(.C(clk), .Q(sync_clk_out),

.D1(1'b0), .D2(1'b1),

.SR(1'b0));

ODDRE1 ODDR_data_ins [7:0]

(.C(clk), .Q(data_out),

.D1(data), .D2(data),

.SR(1'b0));

always @(posedge clk)

data <= data + 1;

endmodule

この方法により、 data と clock が確実に整列されます。 output DDR registers の明示的な instantiation により、 IOB registers が使用されることも保証されます。この方法の唯一の欠点は、各 FPGAに固有であることです。

output DDR registers の動作は予想外で混乱を招く可能性があることに注意してください。たとえば、 @data は @clkの positive edge と同期していることに注意してください。ただし、 ODDRE1 は両方の clock edgesでアクティブです。 2 つの data inputs がいつどのようにサンプリングされるかについては、 FPGA のドキュメントを必ずお読みください。

また、この例では reset が使用されていないことにも注意してください。これは、特に洗練された FPGAsでは安全ではない可能性があります。 output DDR register は、 IOB内のより複雑な logic element の一部にすることができます。このような logic element は、 resetがないと正しく動作しない場合があります。

Timing constraints

では、この方法では timing constraints が必要ですか? IOB registersのおかげで、 clock output と data outputs がほぼ完璧に揃っていれば、それで十分ではないでしょうか。

答えは、この方法は timing constraintsがなくても問題なく機能する可能性があるということです。ただし、それでも timing constraints を利用することをお勧めします。理由は、 IOB registersに関するページの同じトピックと同じです。

その他の考慮事項

ただし、 IOB registers を使用することだけが保証されるわけではありません。 output ports間の物理的な距離にも注意してください。 output ports が互いに離れている場合、この物理的な距離が FPGA上の clock skew に悪影響を及ぼす可能性があります。 traces の長さの違い (つまり、 PCB上の wires ) も悪影響を及ぼす可能性があります。さらに、電気パラメータ (voltage、 I/O standard、 slew rate、 drive current など) は、すべての outputsで同じである必要があります。

FPGA に IOB registersがない場合、 timing constraints が重要になります。 source-synchronous outputs を使用するための基本は、関連するすべての output ports間で低い skew を確保する機能です。通常、 flip-flop と I/O pin の間で delay を制御するだけで十分です。 この delay が、関連する FPGAで可能な最小値に近い場合、 outputs 間の差はほとんどの目的に対して十分に小さくなります。

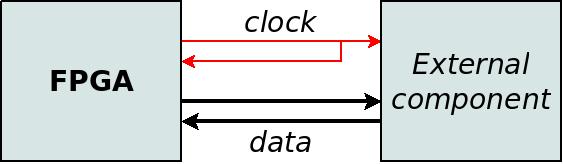

双方向 I/O

source-synchronous outputs の主な特徴は、関連する clock が FPGAによって生成されることです。これは明らかに、すべての data signals が外部コンポーネントに向けられている場合に適しています。ただし、両方向に data signals がある場合でも、 FPGAによって生成された clock に依存することは理にかなっています。

ただし、 data inputs は PCB上の clock と同期しており、 FPGA chip内の clock とは同期していないことに注意してください。もちろん、これら 2 つの clocks には、まったく同じ frequencyがあります。ただし、 output portsの clock-to-output delay によってタイミングに差があります。これは数ナノ秒になることがあります。

したがって、 PCBで loopback を作成することをお勧めします。 FPGAの clock output を input portに接続します。この input port は、 system synchronous clockであるかのように扱うことができます。 外部コンポーネントは、その clock が FPGAからではなく、専用の oscillatorからのものであるかのように動作します。 FPGA と外部コンポーネントの両方が PCB上の同じ物理 signal に依存しているため、これはsystem synchronous clockに似ています。

data inputs をsource-synchronous inputsとして扱うことも可能です。特に、 phase shifting 手法を使用する場合、 clock loopbackは必要ありません。実際、これは DDR SDRAM memoriesとのインターフェースの通常の方法です。

重要な結論は、 PCB を製造する前に input signals の timing を慎重に計画し、必要に応じて clock loopback を追加することを検討することです。