このページは、 timingに関する一連のページに属しています。

このページについて

logic designのいくつかの基本的なトピックを知らずに、 timing を正しく行うことは不可能です。このページでは、このシリーズの残りのページの基礎となるいくつかの基本的な概念について説明します。

以下に書かれていることはすべて、 logic designに関するアカデミック コースで教えられています。ただし、 FPGAs を使用しているすべての人がこの種のコースを受講しているわけではなく、そのようなコースを受講した人でさえ、すべてを覚えているとは限りません。このページは、欠落している部分があればそれを埋めることを目的としています。

このページですでに知っている部分は飛ばしてもかまいませんが、たとえ表面的なものであっても、すべてを読むことをお勧めします。このページの最後のセクションは、このシリーズの次のページを理解するために特に重要です。

簡単なレビュー

timingに関連する概念に入る前に、 logic designに関連するいくつかの用語を簡単に確認します。これらの用語のいずれかがまだ知られていない場合は、このページに進む前によく知っておくことをお勧めします。

まずは combinatorial logic。この用語は、 logic gatesなどの要素を説明するために使用されます。 AND gate、 OR gate、 NOT gateなど。これらの logic elements はメモリがないため、 combinatorial logic と見なされます。言い換えれば、彼らの行動は過去に何が起こったかに依存しません。これらの logic elements の output での値は、 inputsでの値のみに依存します。

combinatorial logic の重要なタイプは look-up table (LUT) です。これは、複数の inputsに依存する任意の logic function を実装する多目的 logic elementです。 LUT は、 FPGA内のほぼすべての combinatorial logic に使用されるため、重要です。 FPGA 内の LUTs は asynchronous ROMs (つまり、 clockなしの ROMs ) として実装されます。 inputs は、 LUT内のデータに対して address として処理されます。 output は通常、1 つまたは 2 つの bitsで構成されます。

これらの LUTs に対する inputs の数は、市場に出回っているほぼすべての FPGAs で 4 または 6 であるため、各 LUT のメモリ セルの数は 16 または 64のいずれかになります。

次に重要な用語は sequential logicです。これには、 flip-flops、 synchronous RAMs、および動作するために clock を必要とする他の多くのビルディング ブロックが含まれます。これらすべての logic elements は、 clockの特定の変更に対する反応としてアクティブになります。これらのアクティビティの瞬間の間、 sequential elements は inputsを無視し、内部状態を保持し、 outputsを変更しません。

たとえば、 clock がローからハイに変わると、 positive edge triggered logic elements がアクティブになります。つまり、 rising clock edgeです。同様に、 clock がハイからローに変化すると、 negative edge triggered logic elements がアクティブになります。つまり、 falling clock edgeです。 clock edgesの両方でアクティブな logic elements もありますが、そのような logic elements は、ほとんど I/O signals のサンプリングまたはそれらの生成にのみ使用されます。

すべての sequential elements には何らかのメモリがあります。これは、 clock edge が到着するまで output を変更しないという事実からの即時の結論です。一部の sequential elements には最小量のメモリがあり、各 outputに対して正確に 1 つの bit メモリです。 shift registers や RAMsなど、他の sequential elements にはより多くのメモリがあります。

timingについて議論するために、重要な事実が 2 つだけあります。 input は clock edgeと組み合わせてのみサンプリングされ、 output はほとんど clock edgeの結果としてのみ変更されます。 sequential elements には asynchronous reset inputがあるという例外が 1 つだけあります。この input がアクティブな場合 ( logic elementに応じてハイまたはロー)、 sequential element の内部状態は、 clockに関係なく、事前定義された値に即座に変更されます。その結果、この要素の一部またはすべての outputs もすぐに既知の値に変更されます。

FPGAでは、一部の sequential elements には asynchronous resetがあり、他の sequential elements にはありません。 asynchronous reset は、 FPGA上のほとんどすべての sequential elements で可能な唯一の asynchronous input です。これは、 logic design の理論には、 S-R flip-flopなどの複数の asynchronous inputsを持つ複数の elements が含まれているにもかかわらずです。

これからは flip-flopsの話

簡単にするために、すべての sequential elements は positive edge triggered flip-flops、つまり clockの rising edge に反応してアクティブな flip-flops であると仮定します。つまり、すべての sequential elements は、ここでは flip-flopsで表されます。これらの flip-flops は inputs に応答し、 clock がローからハイに変化した場合にのみ outputs を更新します。

この方法で timing を理解しやすくなり、 flip-flop に関する議論は他の sequential elementに簡単に一般化できます。

Setup および hold

flip-flop が正しく確実に動作するためには、その inputs が 2 つの timing requirementsに従って安定している (つまり、値が変化しない) 必要があります。

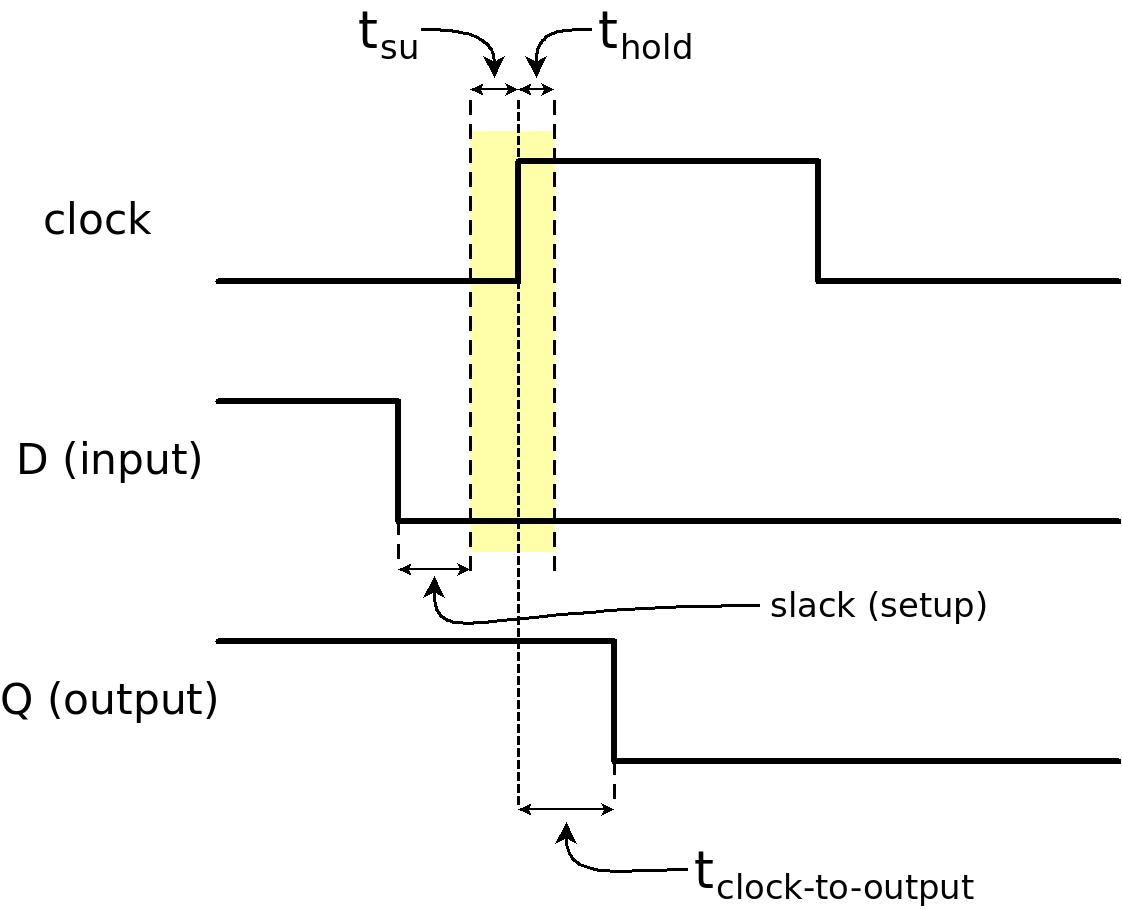

- input は、 clock edgeより前の期間、安定している必要があります。この時間は setup timeと呼ばれ、 tsuとマークされます。

- input は、 clock's edgeの後しばらくの間、安定している必要があります。この時間は hold timeと呼ばれ、 tholdとマークされます。

上の図は、 tsu と tholdの意味を示しています。 D input は、黄色でマークされた期間内で値を変更することはできません。この例では、 D は正当な timingと共にハイからローに変化します。つまり、この黄色の期間外です。

これら 2 つの timing parameters を理解する 1 つの方法は次のとおりです。 input から flip-flop への変更が clock edgeとまったく一緒に変更された場合、 flip-flop がその input を高または低として扱うかどうかは不明であることは明らかです。それは何を選ぶべきですか? clock edge の直前か直後か?

では、 input が clock edgeと「正確に同時に」変更されたということはどういう意味なのかと疑問に思うかもしれません。それはどの程度正確なのでしょうか? 2 つの timing parameters、 tsu 、 thold は、 clock edge からどの程度離れて inputの値を変更しても安全であるかを定義します。これらのパラメーターは、すべての sequential elements に対して同じ意味で定義されています。

この timing requirement に違反した場合、結果は clock edge の後の flip-flop の output がランダムであるというだけよりもずっと悪くなる可能性があることに注意することが重要です。その主な理由は次の 2 つです。

- 場合によっては、プロジェクトの implementation 中に、特に fan-outを削減するために、 FPGA tools が logic design の flip-flops を自動的に複製します。これにより、この flip-flopの値に依存する logic の一部が 1 つの flip-flopに接続され、 logic の別の部分が 2 番目の flip-flopに接続されます。両方の flip-flops が常に同じ output を持つ限り、これは問題ありません。ただし、 timing requirements (tsu と thold) が違反されている場合、これら 2 つの flip-flops のそれぞれが outputsで異なる値を持つ可能性があります。

- flip-flop は、 timing requirements に違反すると、 metastabilityの状態になることがあります。この状態では、 flip-flop の output は、しばらくの間、高くも低くもありません。 metastability とその悪影響の詳細については、このページを参照してください。

Clock-to-output

すべての sequential elements に対して定義されている 3 番目の timing parameter は、 clock-to-output 時間です。これには、 tcko、 tco、 tC_Q など、いくつかの共通シンボルがあります。このパラメーターは timing requirementではありません。むしろ、このパラメーターは、 the sequential element の output (Q) が有効であることが保証される時期を示します。より正確には、 clock edge の何時間後に output が有効になるかを示します (上記の timing diagram を参照)。

実際、この問題には 2 つのパラメーターがあります。

- 最大 clock-to-output: clock edgeから output が有効になるまでの時間。

- 最小限の clock-to-output: clock edgeの後、 output が変更されないことが保証される時間。

ほとんどの場合、最大の clock-to-output だけが興味深いので、このパラメーターが datasheet で指定された場合、ほぼ確実に最大値になります。

flip-flopの timing requirements (tsu と thold) に違反した場合、 output が安定する時期については保証されないことに注意してください。この場合、 flip-flop がしばらくの間未定義の状態 (metastability) のままになる可能性があるため、最大の clock-to-output parameter は意味がありません。

tsu と thold は負になる可能性があります

上の図では正の tsu と tholdを示していますが、これらのパラメーターの一方または両方が負の値である可能性があります。実際、 FPGAs 内の flip-flops は、非常に小さい負の数ではありますが、両方のパラメーターが負であることがよくあります。

たとえば、負の tsu は、 clock edge が到着したときに data が安定している必要がないことを意味します。むしろ、 data は clock edgeの少し後に安定した値に達したに違いありません。しかし、 tsu は、 clock edgeの後でも、その量に制限を設けています。

同様に、負の thold により、 data が clock edgeの前に変更されます。繰り返しますが、これが許可されるまでの量にはまだ制限があり、これは tholdに反映されています。

tsu と thold はどちらも負の値になる可能性があるため、理論的には意味のない timing requirements を定義することが可能です。たとえば、 tsu によって安定することが要求される前に thold によって input が変更されることを許可する場合、これは意味がありません。もちろん、実際の timing 仕様では、このようなことは決して起こりません。 仕様では、 input が安定している必要がある特定の期間を定義する必要があります。そのような期間がない場合、 flip-flop はいつ inputをサンプリングしますか?

clock-to-output parameter は常に正です: flip-flop は、到着する前に clock edge に対応することはできません。

Propagation delay

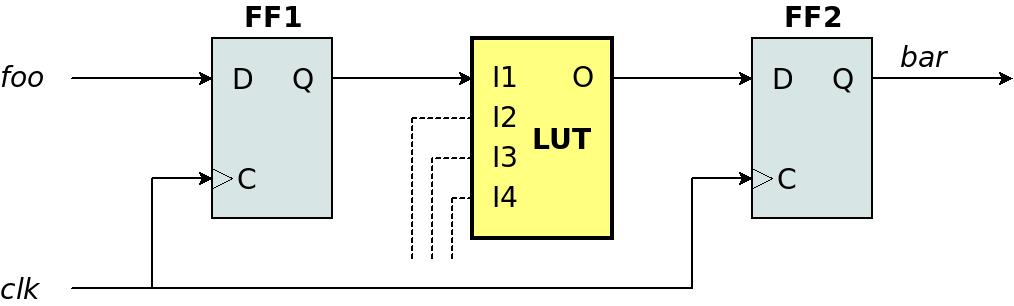

上の図は、中央に LUT がある 2 つの flip-flops 間の単純な接続を示しています。簡単にするために、 LUTの output は I1のみに依存していると仮定しましょう。たとえば、この logic は次の Verilog コードの結果である可能性があるため、 LUT は NOT gateを実装します。

always @(posedge clk)

begin

foo_reg <= foo; // FF1 = foo_reg

bar <= !foo_reg; // FF2 = bar

end

両方の flip-flops が同じ clockに接続されていることに注意してください。この clockの最大周波数は?

この質問に答えるには、不足している情報があります。 FF1の output の値が安定してから、 FF2の input の値が安定するまでの時間は?時間を tpd (propagation delay) としてマークします。

propagation delay という用語は、常に combinatorial logicの特定の segment に関連していることに注意してください。関連する segment を明示的に定義することが重要です。たとえば、 LUTの I1 から同じ LUTの O まで ( input から outputまで) の時間を propagation delayとして定義することもできます。この delay は、以前の tpdの定義とはおそらく異なります。

特に、 FPGAでは、 FF1 の output と LUTの input の間に routing delay があります。したがって、実際には、 FF1の Q は LUTの I1と同じポイントではなく、 signal がこれらの 2 つのポイント間を伝播するのに時間がかかります。

このあいまいさのために、 FPGAsの datasheets にシンボル tpd が表示されることはほとんどありません。そして、そのような datasheetsで propagation delay が指定された場合、通常、このパラメーターの正確な意味が明示的に記述されます。

clockの最大周波数については後で説明します。

path

pathを簡潔に定義することは困難ですが、その例はすでに見てきました。上記で、 FF1の Q と FF2の Dの間の propagation delay として tpd を定義しました。この tpd は、特定のシナリオに関連しています。 FF1 がその値を変更し、更新された値が LUTに到達し、その後 LUT が outputを変更し、最終的に更新された値が FF2に到達します。この一連のイベントは、1 つの signal (FF1の output) のみの変更によって開始され、別のポイント (FF2の input) にある signal が安定したときに終了します。

したがって、 tpd は、 FF1の Q から FF2の Dまでの path の propagation delay として定義されます。または略して、 FF1 から FF2への path 。

path は、このシーケンスの最初から最後まで delay を引き起こすすべての要素で構成されます。 pathには 2 種類の要素があります。

- 電子回路が outputsで signals を更新するまでに時間がかかるため、 delay に貢献する combinatorial logicの要素。これはしばしば logic delayと呼ばれます。上記の例では、 LUT がこの種の要素です。

- Routing.これは、 logic elements間の単なる配線です。これらの segments は、 signal が空間を移動するのに時間がかかり、また電圧の変化が途中で capacitors を充電することを伴うため、 delay に寄与します。

path の目的は、その propagation delayを計算することです。この計算結果がどのように使用されるかを次に示します。

多くの場合、 path は、1 つの flip-flopの output が変更され、別の flip-flopの input につながる特定のルートをたどる理論的な実験を表しています。この理論的な実験では、最初の flip-flop の output が変化したときに仮想のストップウォッチが開始されます。 2 番目の flip-flop の input が変わると、このストップウォッチは停止します。

この理論的な実験は、このストップウォッチが示す時間が長すぎるかどうか、つまり tsu の要件に違反していないかどうかを調べるのに役立ちます。 2 番目の質問は、この時間が短すぎるため、 thold に違反していないかどうかです。

path のルートには、配線と combinatorial logicのみが含まれることに注意してください。したがって、 signal が宛先で安定するまでにかかる時間は、 pathに沿った combinatorial logic と routing の要素のみに依存します。この理論的な実験は、いつ行われても結果は常に同じです。

実際の FPGA designでは、通常、各 flip-flop には、その inputに到達する多くの paths と、その outputで始まる多くの paths があります。実際、 flip-flops のペアの間に複数の path が存在する場合もあります。それでも、 timing の計算は常に、1 つの flip-flop だけが outputを変更したという前提で行われ、 FPGAの logic で発生するすべてのことは、その変更の直接的な結果です。 FPGA design で計算される paths の数は膨大になる可能性がありますが、これはもちろんソフトウェアによって自動的に行われます。

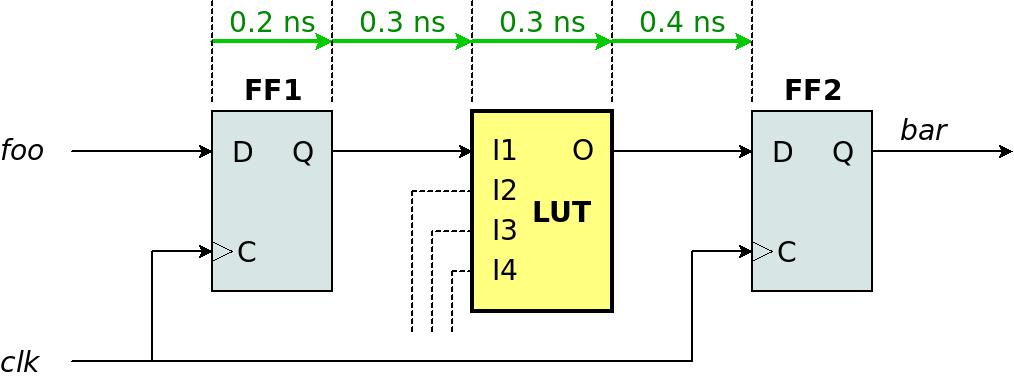

シンプルな static timing analysis

デモンストレーションのために、上記の例の単純な timing analysis を 2 つの flip-flopsで作成します。 timing constraints のトピックについては後で説明しますが、差し当たり、 @clk の周波数が 250 MHz (4 ns) であり、 logic に直接接続されている (つまり、実際の designでは推奨されない PLLなし) と仮定します。 、しかしこれは timing analysisを簡素化します)。 timing constraint ( SDC スタイル) は次のようになります。

create_clock -period 4.000 -name clk [get_ports clk]

実際の timing analysis の例はこのシリーズの次のページに示されていますが、その分析は正確であるため、理解しにくい詳細が多数含まれています。したがって、これは原理を示すだけの簡単な分析です。

分析では、前述の理論的な実験が実行されます。 @clkの rising edgeと一緒にスタートする架空のストップウォッチ。これは一連のイベントと、各イベントが寄与する (架空の) delay です。

- FF1 のClock-to-output (0.2 ns): FF1の output (Q) が flip-flopの input (D) の値で更新されるまでにかかる時間。

- Routing delay から I1 (0.3 ns): signal が FF1の output から LUTの input (I1) に移動するのにかかる時間。

- LUTの propagation delay (0.3 ns): LUT は、 inputs (この場合はI1 ) のいずれかが変更された後、 output (O) を更新するためにこの時間を必要とします。

- Routing delay から FF2の input (0.4 ns): signal が LUTの output から FF2の input に移動するのにかかる時間 (D)

この path の propagation delay (tpd) は、これらすべての delaysの合計です。 0.2 + 0.3 + 0.3 + 0.4 = 1.2 ns.例として、 FF2の tsu が 0.1 nsであるとします。これは、 FF2の input (D) が @clkの次の rising edge の前に安定した 0.1 ns でなければならないことを意味します。つまり、許可される最大 tpd は 4 - 0.1 = 3.9 nsです。

しかし、 tpd はあくまでも 1.2 nsなので、この計算によると、 path は timing constraint を大幅に上回っています。このマージンは slackと呼ばれ、この場合は 3.9 - 1.2 = 2.7 nsです。この数値がソフトウェアの timing 計算に表示される場合、ツールが timing constraints を達成するのに苦労したかどうかを示します。 slack がゼロに近い場合、多くの場合、 path を timing requirementsに適合させるためにソフトウェアが多大な労力を費やしたことを示しています。

propagation delay では、この path が timing を達成できる @clk の最大周波数を計算することもできます。 tpd は 1.2 nsであり、 tsu の要件は、次の rising edge が 0.1 ns の後に到着できることを意味します。つまり、 rising edgesの間に少なくとも 1.3 ns が必要です。これは、約 769 MHzの周波数を意味します。これは非常に高い周波数ですが、 path には LUTが 1 つしか含まれていないため、現実的な結果です。実際の logic は通常、それよりも複雑です。そのため、実際の周波数はしばしばはるかに低くなります。

実際の static timing analysis ではこの計算が正確に行われますが、これは話の一部にすぎません。ここで計算された path は、実際の計算ではdata pathと呼ばれます。ただし、実際の static timing analysis では、 clock edge が両方の flip-flops にまったく同時に到着しないことも考慮されます。これは、 clock buffer からこれらの各 flip-flops への delay がわずかに異なるためです。これらの delays 間のこの違いは clock skewと呼ばれます。また、 clock jitterのため、各 clock edge 間の時間はまったく同じではありません。 clock のこれらの問題により、次のページに示すように、正確な計算がより複雑になります。

Recovery および Removal

flip-flop に asynchronous reset input がある場合 (本当にそれが必要ですか?)、この input が非アクティブになるタイミングに関する要件があります。 flip-flop はいずれにせよ既知の状態に変わるため、 reset がいつアクティブになるかは問題ではないことに注意してください。

しかし、 reset が非アクティブになると、 flip-flop は clockに敏感になり始めます。この reset の非アクティブ化が clock edgeの近くで発生した場合、 flip-flop がそれに応答する必要があるかどうかは明確ではありません。 tsetup および tholdと同様に、 reset は clock edgeの前後の期間中安定している必要があります。または、より具体的には:

- reset は、 clock edgeの前の期間中にアクティブから非アクティブに変更してはなりません。この時間は recovery timeと呼ばれます。これは、 flip-flop が reset から回復し、 clock edgeの準備が整うまでにかかる時間です。

- reset は、 clock's edgeの後の一定期間、アクティブから非アクティブに変更してはなりません。この時間はremoval timeと呼ばれます。

これらの定義は、 tsetup および tholdの定義に似ています。それは偶然ではありません: recovery time は、 setup timeの特別な種類です。 timing analysis も同じ方法で行われます。唯一の違いは、 data signalの値に関係なく、 setup time が関連することです。対照的に、 asynchronous reset signal がアクティブに変更された場合、 recovery time は適用されません。 removal time と hold time の関係は同じです。

この類似性のため、 Recovery と Removal については、これ以上説明しません。また、上記は asynchronous resetだけでなく、すべての asynchronous inputsに当てはまることに注意してください。

RTL paradigm および timing

上に示した 2 つの flip-flops の例は単純ですが、 RTL paradigmで作成されたすべての logic を表しています。 各 path は flip-flop で始まり、同じ clock (または related clock) を持つ flip-flop で終わります。 path 自体は、 combinatorial logic と routingで構成されています。この例では、 combinatorial logic は 1 つの LUTだけですが、これと pathの複数の logic elements の間に実質的な違いはありません。構造は同じです。

RTL paradigm が非常に重要な理由は、この方法を使用すると、ほとんどすべての data paths が同じ単純な構造を持っているからです。また、 logic design 内の paths の数は多くの場合膨大な数になるため、 timing analysis のシンプルさがミスの防止に役立ちます。とりわけ、 timing analysis が特定のパターンを持っているという事実により、 timing report を読み取って、意味があるかどうかを尋ねることができます。

したがって、可能な限り、すべてを sequential element で開始し、 sequential elementで終了する必要があります。これは、 Verilog コードを書くとき、および logicの構造を一般的に計画するときに役立つガイドラインです。

これで、 timing constraintsの背後にある理論の簡単な紹介を終わります。 clock period constraint および関連する timing reports については、次のページで説明します。